Zrozumienie ISPPAC-CLK5320S-01TN64C Programowalny generator zegara

ISPPAC-CLK5320S-01TN64C to programowalny generator zegara zaprojektowany w celu zarządzania i rozpowszechniania sygnałów zegarowych z precyzją.Oferuje wiele wyjść, regulowane częstotliwości i niski poziom, co czyni go doskonałym wyborem dla aplikacji wymagających dokładnego czasu.Dzięki wbudowanej technologii pętli o długości faz (PLL) zapewnia niezawodną synchronizację w różnych komponentach.Urządzenie obsługuje różne standardy zegara i umożliwia łatwe dostosowywanie, dzięki czemu nadaje się do szerokiej gamy systemów.Niezależnie od tego, czy potrzebujesz buforowania zerowego opóźnienia, podziału częstotliwości, czy elastycznego routingu sygnału, ten generator zegara zapewnia potrzebną wydajność.Zawiera także obsługę JTAG dla programowania w systemie, upraszczając konfigurację i konfigurację.W tym artykule eksploruje jego funkcje, funkcje, aplikacje i szczegóły techniczne.Katalog

Przegląd ISPPAC-CLK5320S-01TN64C

. ISPPAC-CLK5320S-01TN64C jest wszechstronnym, programowalnym buforem zerowym zerowym opóźnieniem zaprojektowanym do aplikacji dystrybucji zegara.Oferuje do 12 ultra-niskich wyjść, przy czym każda para wyjściowych jest możliwa do obsługi różnych standardów we/wy, takich jak LVTTL, LVCMOS, SSTL i HSTL.Użytkownicy mogą dostosowywać częstotliwości wyjściowe, zakończenie, stawki zaliczające i czasy czasowe niezależnie dla każdego wyjścia.

Dzięki wysokiej wydajności PLL to urządzenie zapewnia minimalne opóźnienie propagacji.Zawiera trzy programowalne 5-bitowe liczniki do generowania wielu częstotliwości, które można kierować do dowolnego pinu wyjściowego.Urządzenie oferuje cztery tryby działania, w tym opcje bufora opóźnienia zero-opóźnienia i niezerowej opóźnienia.

Niezależnie od tego, czy potrzebujesz wielkości jednej jednostki, czy masowej, ISPCLOCK5300S-01TN64C zapewnia niezawodne, elastyczne rozwiązania do zarządzania zegarami.Skontaktuj się z nami w celu uzyskania opcji zakupu masowego i skorzystaj z naszych konkurencyjnych cen!

Szczegóły pinout ISPPAC-CLK5320S-01TN64C

Kluczowe funkcje ISPPAC-CLK5320S-01TN64C

Cztery konfiguracje operacyjne

ISPPAC-CLK5320S-01TN64C oferuje cztery elastyczne tryby pracy, co pozwala wybrać najlepszą konfigurację potrzeb dystrybucji zegara.Tryb bufora opóźnienia zerowego synchronizuje zegary wejściowe i wyjściowe z minimalnym opóźnieniem, podczas gdy tryb bufora opóźnienia zerowego i niezerowy opóźnienie łączą obie funkcje, aby zwiększyć elastyczność.Podwójny niezerowy tryb bufora opóźnienia zapewnia dwie niezależne ścieżki opóźnienia, a niezerowy bufor opóźnienia z trybem podziału wyjściowego pozwala na podzielone wyjścia zegara z niestandardowymi regulacjami czasu.

Szeroki zakres częstotliwości wejściowych i wyjściowych

Dzięki obsłudze częstotliwości od 8 MHz do 267 MHz, to urządzenie zapewnia szeroki zakres opcji taktowania, co sprawia, że nadaje się do różnych aplikacji rozrządu.Niezależnie od tego, czy Twój system wymaga sygnałów o niskiej lub wysokiej częstotliwości, ta elastyczność zapewnia bezproblemową działanie na różnych urządzeniach.

Niski skoś i drganie do precyzyjnego momentu

To urządzenie zapewnia precyzyjne czasy sygnału z skośnym skośnięciem wyjściowym mniej niż 100ps i pod jitterem szczytowym do szczytu 70ps.Te niskie wartości pomagają utrzymać integralność sygnału i minimalizować błędy czasu w aplikacjach o dużej prędkości, zapewniając płynne działanie w złożonych obwodach.

Do 20 programowalnych buforów fan-out

ISPPAC-CLK5320S-01TN64C zapewnia do 20 niezależnie programowalnych buforów, co zapewnia pełną kontrolę nad konfiguracją wyjściową.Obsługuje wiele jedno-końcowych standardów wyjściowych, w tym LVTTL, LVCMOS, HSTL, EHSTL i SSTL.Możesz dostosować impedancję wyjściową między 40 Ω do 70 Ω w przyrostach 5Ω i modyfikować prędkość notatki dla lepszych przejść sygnału.Dodatkowo urządzenie ma do 10 banków wyjściowych, każdy z własnym zasilaczem (1,5 V, 1,8 V, 2,5 V lub 3,3 V), umożliwiając oddzielne poziomy napięcia dla różnych wyjść.

PLL o wysokiej wydajności

Zintegrowany PLL zapewnia stabilne i niezawodne sygnały zegara z programowalnym wykrywaniem blokady w celu monitorowania dokładności.Obejmuje trzy programowalne dzielniki wyjściowe, które działają w mocy 2 (1, 2, 4, 8, 16, 32), ułatwiając regulacje częstotliwości.Filtr pętli na chipie pomaga zmniejszyć szum, a kompatybilność zegara spektrum spektrum minimalizuje zakłócenia elektromagnetyczne.Urządzenie obsługuje zarówno wewnętrzne, jak i zewnętrzne informacje zwrotne, oferując elastyczne opcje synchronizacji zegara.

Precyzyjna regulacja fazy

Możesz dopracować każde wyjście z ± 5NS regulacji fazowej, aby dokładnie wyrównać sygnały.Urządzenie zapewnia osiem programowalnych ustawień fazowych o minimalnym stopniu wielkości 156PS, zapewniając precyzyjną kontrolę czasu.Obsługuje gruboziarniste i drobne tryby regulacji, umożliwiając spełnienie różnych wymagań systemowych.

Wiele domen częstotliwości zegara

ISPPAC-CLK5320S-01TN64C obsługuje maksymalnie trzy oddzielne domeny częstotliwości zegara, umożliwiając wydajne zarządzanie wieloma sygnałami czasu w jednym urządzeniu.Ta funkcja jest idealna dla systemów, które wymagają niezależnych źródeł zegara dla różnych komponentów.

Elastyczne wejścia zegara i informacje zwrotne

To urządzenie zapewnia szereg programowalnych standardów wejściowych i sprzężenia zwrotnego, w tym LVTTL, LVCMOS, SSTL, HSTL, LVDS, LVPECL, Różnicowego HSTL i SSTL różnicowego.Multiplekser wyboru zegara A/B umożliwia przełączanie między źródłami wejściowymi, podczas gdy programowalna ścieżka sprzężenia zwrotnego obsługuje LVTTL, LVCMOS, SSTL i HSTL.Ponadto wbudowane programowalne zakończenie upraszcza zarządzanie sygnałami, zwiększając ogólną wydajność.

Zgodność z gorącym gniazdem

ISPPAC-CLK5320S-01TN64C jest zgodny z gorącym gniazdem, co oznacza, że wszystkie wejścia i wyjścia pozostają w pełni funkcjonalne nawet podczas zamiany na gorąco.Zapewnia to ciągłe działanie bez ryzyka utraty danych lub przerwy.

Programowanie JTAG i system

Urządzenie obsługuje skanowanie granic JTAG i programowanie w systemie, ułatwiając konfigurację i testowanie bez konieczności usuwania go z obwodu.Upraszcza to debugowanie i przyspiesza czas rozwoju.

Silna odporność na hałas

To urządzenie, zaprojektowane tak, aby wytrzymać szum zasilający, zapewnia stabilną i niezawodną obsługę nawet w środowiskach elektrycznych.To sprawia, że jest to idealny wybór dla aplikacji o wysokiej wydajności, które wymagają precyzyjnego zarządzania zegara.

Opcje temperatury i opakowania

ISPPAC-CLK5320S-01TN64C jest dostępny zarówno w zakresie komercyjnym (od 0 ° C do 70 ° C), jak i przemysłowej (-40 ° C do 85 ° C), zapewniając niezawodną wydajność w różnych warunkach środowiskowych.Występuje w 48-pinowych i 64-pinowych pakietach TQFP, co ułatwia integrację z różnymi systemami.

Specyfikacje techniczne

Specyfikacje techniczne półprzewodnika sieci, ISPPAC-CLK5320S-01TN64C.

|

Atrybut |

Wartość |

|

Producent |

Semiconductor kratowy |

|

Szereg |

ISPCLOCK ™ |

|

Typ |

Generator zegara, dystrybucja fanout, bufor zero opóźnienia |

|

Liczba obwodów |

1 |

|

Napięcie - zasilanie |

3V ~ 3,6 V. |

|

Temperatura operacyjna. |

0 ° C ~ 70 ° C. |

|

Częstotliwość - maks |

267 MHz |

|

Współczynnik - wejście: wyjście |

2:20 |

|

Pll |

Tak z obwodnicą |

|

Dzielnik/mnożnik |

Tak/Nie |

|

Różnica - wejście: wyjście |

Tak/Nie |

|

Wejście |

HSTL, LVCMOS, LVDS, LVPECL, LVTTL, SSTL |

|

Wyjście |

EHSTL, HSTL, LVCMOS, LVTTL, SSTL |

|

Pakiet / obudowa |

64-lqfp |

|

Pakiet dostawcy |

64-TQFP (10x10) |

|

Typ montażu |

Mocowanie powierzchniowe |

|

Pakiet |

Taca |

|

Podstawowy numer produktu |

ISPPAC-CLK53 |

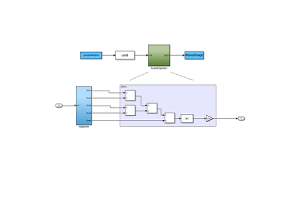

Funkcjonalny schemat blokowy ISPPAC-CLK5320S-01TN64C

Schemat pokazuje, jak ISPPAC-CLK5320S-01TN64C działa jako programowalny generator zegara.Występuje wiele sygnałów zegara odniesienia (RefA, RefB) i sygnału sprzężenia zwrotnego (FBK), aby utrzymać wszystko zsynchronizowane.Wejście wyboru (Refsel) wybiera, które odniesienie do użycia.Detektor fazowy porównuje wybrane odniesienie z sygnałem sprzężenia zwrotnego, a filtr pętli wygładza wszelkie zmiany przed przejściem sygnału do oscylatora kontrolowanego napięcia (VCO).VCO generuje zegar wysokiej częstotliwości, który jest następnie podzielony na różne wyjścia zegara.Wyjścia te przechodzą matrycę routingu, w której można je dostosować do czasu (sterowanie Skew) przed wysłaniem sterowników wyjściowych.System zawiera również elementy sterujące Włącz wyjście, opcję obejścia PLL i funkcję wykrywania blokady, aby pokazać, gdy wszystko jest stabilne.Ponadto do programowania i testowania jest uwzględniany interfejs JTAG.Ta konfiguracja zapewnia dokładny rozkład zegara w różnych częściach systemu, dzięki czemu jest przydatny dla procesorów, urządzeń komunikacyjnych i innych obwodów cyfrowych.

Zastosowania i zastosowania ISPPAC-CLK5320S-01TN64C

Płytka drukowana wspólny rozkład zegara

ISPPAC-CLK5320S-01TN64C jest szeroko stosowany do dystrybucji wspólnego sygnału zegara na płytkach obwodów.Zapewnia, że wszystkie połączone komponenty otrzymują synchronizowane sygnały taktowania, poprawiając komunikację między różnymi częściami systemu.Dzięki niskiemu skośnemu i jitterowi pomaga utrzymać dokładność sygnału, zmniejszając błędy w transferie danych.

Generowanie częstotliwości oparte na PLL

To urządzenie ma wysokowydajny PLL, umożliwiający generowanie stabilnych i programowalnych częstotliwości zegara.Niezależnie od tego, czy musisz się pomnożyć, dzielić lub synchronizować częstotliwości, ISPPAC-CLK5320S-01TN64C zapewnia elastyczne zarządzanie zegarami dla szeregu aplikacji, w tym przetwarzania danych, systemów komunikacyjnych i urządzeń osadzonych.

Bufor zegara o wysokim fanach

Gdy pojedynczy sygnał zegara musi napędzać wiele komponentów, ISPPAC-CLK5320S-01TN64C działa jako niezawodny bufor o wysokim wentylatorze.Przy maksymalnie 20 programowalnych wyjściach może efektywnie rozpowszechniać sygnały zegara przy jednoczesnym zachowaniu niskiego pochylenia między wyjściami.Jest to przydatne w dużych systemach, w których wiele podsystemów wymaga zsynchronizowanego zegara.

Bufor zegara o zerowej opóźnieniu

Funkcja buforu o zerowym opóźnieniu ISPPAC-CLK5320S-01TN64C zapewnia, że zegar wyjściowy pozostaje wyrównany z zegarem odniesienia, zapobiegając niedopasowaniu czasów.Jest to szczególnie przydatne w aplikacjach, w których wymagana jest precyzyjna synchronizacja, takie jak interfejsy pamięci, urządzenia sieciowe i szybkie systemy przetwarzania danych.

Zarys Wymiary ISPPAC-CLK5320S-01TN64C

Schemat zawiera wymiary fizyczne i szczegóły układu pakietu ISPPAC-CLK5320S-01TN64C.Zawiera różne widoki-top, dno, bok i przekrój-aby dać wyraźne wyobrażenie o jego kształcie i rozmiarze.Pakiet ma 64 szpilki rozmieszczone wokół jego krawędzi.Widok z góry pokazuje układ pinowy z małym markerem wskazującym pin 1 dla prawidłowej orientacji.Dolna widok zapewnia podobną perspektywę, ale poniżej.

Widok z boku podkreśla wysokość opakowania, kształt przewodów i sposób, w jaki rozciągają się z ciała.Szczegółowe powiększenie (szczegół „A”) pokazuje, w jaki sposób przewody zginają i dotykają płytki drukowanej.Płaszczyzna siedząca to część, która kontaktuje się z płytą po zamontowaniu.

Tabela zawiera różne pomiary, w tym wysokość opakowania, szerokość ołowiu i odstępy między szpinami.Wszystkie wymiary są w milimetrach.Notatki wyjaśniają tolerancje, w jaki sposób mierzony jest pakiet oraz dodatkowe szczegóły, takie jak występy pleśni i wykończenie ołowiu.Dokładny kształt narożników nie jest ustalony, co oznacza, że mogą wystąpić niewielkie zmiany.Ten rysunek zapewnia właściwe dopasowanie i umieszczenie komponentu na płycie drukowanej.

ISPPAC-CLK5320S-01TN64C Alternatywy

|

Numer części |

Producent |

Kluczowe funkcje |

Przypadek użycia/notatki |

|

Semiconductor kratowy |

Podobne do ISPPAC-CLK5320S, ale z 2:16 Współczynnik wejścia do wyjścia.Obsługuje ten sam zakres napięcia, częstotliwość i wiele formatów wyjściowych.Występuje w pakiecie 64-TQFP. |

Nadaje się do dystrybucji zegara w średnią skalę cyfrową systemy, w których 16 wyjść jest wystarczające. |

|

|

Semiconductor kratowy |

Wersja o niższym wyjściu z wskaźnikiem wejścia do wyjścia 2:12. Obsługuje te same funkcje zegara, ale działa w szerszym zakresie temperatur (-40 ° C do 85 ° C).Występuje w mniejszym pakiecie 48-TQFP. |

Najlepsze do zastosowań przemysłowych wymagających solidnego Tolerancja temperatury i umiarkowany rozkład zegara. |

|

|

Semiconductor kratowy |

Oferuje rozkład zegara 8 output z podobnym Zestaw funkcji, w tym PLL, wiele formatów wejściowych/wyjściowych i maks. Częstotliwość 267 MHz.Działa również w zakresie -40 ° C do 85 ° C. |

Zaprojektowany do kompaktowego zarządzania zegarami o wysokiej niezawodności w trudnych środowiskach lub zastosowaniach ograniczonych przestrzenią. |

O półprzewodniku kratowym

Semiconductor Lattice opracowuje programowalne rozwiązania o niskiej mocy, wysokiej wydajności do zarządzania zegara, łączności i przetwarzania.Jako producent ISPPAC-CLK5320S-01TN64C, Lattice zapewnia niezawodną i elastyczną technologię dystrybucji zegara zaprojektowaną do dokładnego czasu i synchronizacji.Koncentrując się na innowacjach i wydajności, Lattice nadal wspiera nowoczesną elektronikę za pomocą zaufanych, wysokiej jakości rozwiązań.

Wniosek

ISPPAC-CLK5320S-01TN64C to elastyczne i niezawodne rozwiązanie zarządzania zegarami zaprojektowanym w celu sprawnego działania systemu.Dzięki programowalnym funkcjom, niskim skośie i wielu opcjom wyjściowym zapewnia dokładny czas dla różnych aplikacji.Niezależnie od tego, czy potrzebujesz buforu zero-opóźnienia, generowania częstotliwości, czy o wysokim fanowii, to urządzenie zapewnia potrzebną wydajność i elastyczność.Jeśli szukasz niezawodnego sposobu zarządzania sygnałami zegara, jest to świetny wybór.

Arkusz danych pdf

ISPPAC-CLK5320S-01TN64C Arkusz danych:

O nas

ALLELCO LIMITED

Czytaj więcej

Szybkie zapytanie.

Proszę wysłać zapytanie, natychmiast odpowiemy.

Często Zadawane Pytania [FAQ]

1. Do czego służy ISPPAC-CLK5320S-01TN64C?

Jest to programowalny generator zegara i bufor wentylatora zaprojektowany do zarządzania i rozpowszechniania sygnałów zegarowych.Pomaga utrzymać różne części systemu zsynchronizowane, zapewniając dokładny czas.

2. Czy mogę niezależnie dostosować częstotliwości wyjściowe?

Tak, urządzenie umożliwia ustawienie różnych częstotliwości wyjściowych za pomocą programowalnych dzielników.Każde wyjście można dostosować, aby dopasować się do określonych potrzeb czasowych.

3. Jakie rodzaje sygnałów zegara obsługuje?

Obsługuje wiele standardów wejściowych i wyjściowych, w tym LVTTL, LVCMOS, SSTL, HSTL, LVDS i LVPECL.To sprawia, że jest kompatybilny z różnymi systemami i urządzeniami.

4. Jak działa tryb buforowy zero-opóźnienia?

W trybie zerowym opóźnienie zegary wejściowe i wyjściowe pozostają wyrównane z minimalnym opóźnieniem.Pomaga to utrzymać synchronizację między różnymi komponentami w obwodzie.

5. Czy obsługuje programowanie w systemie?

Tak, ma interfejs JTAG do programowania i testowania w systemie.Pozwala to skonfigurować go bez usuwania go z obwodu.

PCM vs. Dolby Digital: The Ultimate Guide to High Fidelity i Sound Audio Technologies

na 2025/02/24

Przewodnik zakupu dla EPM7256aeti144-7n wszystko, co musisz wiedzieć

na 2025/02/21

Popularne posty

-

Złożone komputery zestawu instrukcji: Jak zmieniły obliczenia?

na 8000/04/18 147761

-

Pinout i funkcje USB-C

na 2000/04/18 111984

-

Korzystanie z prymitywnych symulacji XILINX: kompleksowy przewodnik po projekcie i symulacji FPGA

na 1600/04/18 111351

-

Napięcia zasilania w elektronice: znaczenie VCC, VDD, VEE, VSS i GND

na 0400/04/18 83743

-

RJ45 Podręcznik złącza: pinout, okablowanie, typy kablowe i zastosowania

na 1970/01/1 79538

-

Ostateczny przewodnik po kodach kolorów drutu w nowoczesnych systemach elektrycznych

Sposób, w jaki nasze systemy elektryczne używają kolorów, nie jest tylko dla wyglądu.Każdy kolor drutu wskazuje teraz określoną funkcję, ułatwiając poprawną identyfikację komponentów elektrycznych ...na 1970/01/1 66946

-

Przewodnik zaworu oczyszczania: funkcja, objawy, testowanie i wymiana w celu optymalnej wydajności silnika

Zawór czyszczenia jest kluczową częścią systemu samochodu, który pomaga utrzymać w czystości powietrza poprzez zarządzanie oparami paliwowymi, zanim będą mogły uciec do atmosfery.To nie tylko pomag...na 1970/01/1 63087

-

Jakość (Q) Współczynnik: Równania i zastosowania

Współczynnik jakości lub „Q” jest ważny podczas sprawdzania, jak dobrze induktory i rezonatory działają w systemach elektronicznych, które wykorzystują częstotliwości radiowe (RF).„Q” mierzy, jak d...na 1970/01/1 63026

-

Osiągnięcie wydajności szczytowej przy maksymalnym twierdzeniu o przeniesieniu mocy

Twierdzenie o maksymalnym przeniesieniu mocy wyjaśnia, w jaki sposób energia ze źródła, takiego jak akumulator lub generator, płynie do podłączonego obciążenia.Pokazuje dokładny warunek, w którym o...na 1970/01/1 54092

-

A23 Specyfikacje i kompatybilność baterii

Akumulator A23 to mała akumulator w kształcie cylindra o wysokim napięciu.Nazywany również 23a, 23E lub Mn21, działa przy 12 woltach i znacznie wyższy niż akumulatory AA lub AAA.Jego specj...na 1970/01/1 52170