Zrozumienie architektury i zastosowań FPGA XC2S200-5FG256I

Być może szukasz programowalnego urządzenia logicznego, które pozwoli Ci kształtować sprzęt cyfrowy dokładnie tak, jak tego potrzebuje Twój system.Układ FPGA XC2S200-5FG256I zapewnia elastyczne bloki logiczne, pamięć wewnętrzną oraz wiele połączeń wejściowych i wyjściowych, dzięki czemu można budować niestandardowe funkcje cyfrowe w jednym urządzeniu.Jego architektura obsługuje routing sygnału, kontrolę taktowania i obsługę interfejsów w wielu typach sprzętu elektronicznego.Dzięki programowalnym trasom i zasobom pamięci dostępnym w chipie można go dostosować do różnych zadań kontrolnych, ścieżek komunikacyjnych i wbudowanych funkcji systemowych bez zmiany sprzętu fizycznego.Katalog

Przegląd XC2S200-5FG256I

The XC2S200-5FG256I to programowalne urządzenie logiczne zbudowane na architekturze Spartan II FPGA i przeznaczone do konfigurowalnych systemów cyfrowych.Zawiera około 200 000 bramek logicznych rozmieszczonych w konfigurowalnych blokach logicznych, które można zaprogramować w celu realizacji niestandardowych funkcji cyfrowych.Zintegrowany blok RAM umożliwia tymczasowe przechowywanie danych, natomiast duża liczba pinów wejściowych i wyjściowych umożliwia elastyczną komunikację z komponentami zewnętrznymi.Urządzenie zasilane jest z rdzenia niskonapięciowego i wytrzymuje przemysłowe warunki temperaturowe.Jego architektura obsługuje prototypowanie sprzętu, kontrolę interfejsów i zadania przetwarzania cyfrowego w wbudowanym sprzęcie elektronicznym.

Szukasz XC2S200-5FG256I?Skontaktuj się z nami, aby sprawdzić aktualny stan magazynowy, czas realizacji i cenę.

XC2S200-5FG256I b

Struktura I/O dzieli obwód urządzenia na osiem banków rozmieszczonych wzdłuż wszystkich czterech boków pakietu FPGA.Każdy bank grupuje zestaw pinów wejściowych i wyjściowych, które korzystają z tego samego zasilania VCCO, umożliwiając przyłożenie stałego poziomu napięcia do wszystkich pinów w tym obszarze.Wejścia zegara globalnego oznaczone od GCLK0 do GCLK3 są umieszczone w pobliżu dolnej i górnej części układu, aby równomiernie rozprowadzać sygnały zegara w wewnętrznym układzie logicznym.Taki układ umożliwia jednoczesne działanie wielu standardów sygnalizacji poprzez przypisanie różnych poziomów napięcia do oddzielnych banków, przy jednoczesnym zachowaniu zorganizowanego trasowania pomiędzy zewnętrznymi pinami i wewnętrzną programowalną logiką.

Model CAD XC2S200-5FG256I

Symbol XC2S200-5FG256I

XC2S200-5FG256I Wymiary

Model 3D XC2S200-5FG256I

Cechy XC2S200-5FG256I

Programowalna architektura logiczna FPGA

Urządzenie wykorzystuje konfigurowalną strukturę logiczną, która umożliwia definiowanie obwodów cyfrowych poprzez programowalne bloki logiczne i ścieżki routingu.Struktura ta pozwala projektantom wdrażać niestandardowe zachowania sprzętu bez modyfikowania urządzenia fizycznego, wspierając elastyczny rozwój systemów cyfrowych i prototypowanie sprzętu.

Zintegrowane zasoby pamięci blokowej

Wewnętrzna blokowa pamięć RAM zapewnia dedykowaną pamięć w programowalnej strukturze.Te bloki pamięci obsługują buforowanie danych, tablice przeglądowe i operacje przechowywania tymczasowego, zmniejszając potrzebę stosowania zewnętrznych komponentów pamięci w wielu zastosowaniach przetwarzania cyfrowego.

Konfigurowalny interfejs wejściowy i wyjściowy

Do 176 pinów wejściowych i wyjściowych użytkownika zapewnia elastyczną łączność z urządzeniami zewnętrznymi.Każdy pin można skonfigurować do różnych funkcji wejściowych, wyjściowych lub dwukierunkowych, umożliwiając urządzeniu interakcję z czujnikami, interfejsami komunikacyjnymi i systemami sterowania.

Programowalna sieć routingu

Programowalna sieć połączeń łączy bloki logiczne, elementy pamięci i interfejsy wejściowe i wyjściowe.Sygnały można kierować konfigurowalnymi ścieżkami, umożliwiając niestandardowy przepływ sygnału między zasobami wewnętrznymi przy jednoczesnym zachowaniu przewidywalnego zachowania cyfrowego.

Zarządzanie zegarem przy użyciu pętli z blokadą opóźnienia

Zintegrowane obwody pętli z blokadą opóźnienia obsługują dystrybucję zegara i wyrównanie taktowania wewnątrz urządzenia.Obwody te pomagają utrzymać stabilne relacje czasowe pomiędzy wewnętrznymi sekcjami logicznymi a zewnętrznymi źródłami zegara.

Możliwość pracy w temperaturze przemysłowej

Urządzenie obsługuje pracę w rozszerzonym zakresie temperatur, odpowiednim dla środowisk przemysłowych.Umożliwia to stabilną pracę w systemach narażonych na działanie zmiennych warunków środowiskowych, takich jak urządzenia fabryczne lub instalacje zewnętrzne.

Kompaktowy pakiet BGA do montażu powierzchniowego

Urządzenie jest pakowane w formacie siatki składającej się z 256 kulek, co umożliwia dużą liczbę połączeń w kompaktowej obudowie.Ten styl opakowania obsługuje gęste układy płytek drukowanych, zachowując jednocześnie niezawodność elektryczną w przypadku urządzeń o dużej liczbie pinów.

Dane techniczne XC2S200-5FG256I

| Atrybut produktu | Wartość atrybutu |

| Producent | AMD Xilinx |

| Napięcie - zasilanie | 2,375 V ~ 2,625 V |

| Całkowita liczba bitów RAM | 57344 |

| Pakiet urządzeń dostawcy | 256-FBGA (17x17) |

| Seria | Spartan®-II |

| Opakowanie/etui | 256-BGA |

| Pakiet | Taca |

| Temperatura pracy | -40°C ~ 100°C (TJ) |

| Liczba elementów/komórek logicznych | 5292 |

| Liczba LAB/CLB | 1176 |

| Liczba wejść/wyjść | 176 |

| Liczba bramek | 200 000 |

| Typ mocowania | Montaż powierzchniowy |

| Podstawowy numer produktu | XC2S200 |

| Stan RoH | Niezgodny z dyrektywą RoHS |

| Poziom wrażliwości na wilgoć (MSL) | 3 (168 godzin) |

| Stan REACH | REACH Bez zmian |

| ECCN | EAR99 |

| HTSUS | 8542.39.0001 |

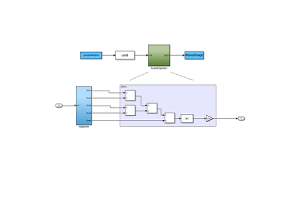

Schemat blokowy XC2S200-5FG256I

Centralna siatka konfigurowalnych bloków logicznych tworzy programowalną strukturę logiczną, w której funkcje cyfrowe są implementowane przy użyciu tablic przeglądowych i przerzutników.Pionowe kolumny oznaczone blokową pamięcią RAM zapewniają wbudowane zasoby pamięci umieszczone obok tablicy logicznej do przechowywania danych i operacji buforowania.Bloki logiczne wejścia i wyjścia wyścielają zewnętrzne krawędzie urządzenia i łączą wewnętrzną sieć routingu z zewnętrznymi pinami.Jednostki pętli z blokadą opóźnienia umieszczone w rogach obsługują wyrównanie zegara i kontrolę taktowania w całej wewnętrznej strukturze logicznej.Ścieżki połączeń między macierzą CLB, kolumnami pamięci, jednostkami zegara i blokami IO tworzą programowalną sieć routingu, która umożliwia elastyczne połączenia sygnałowe w całym urządzeniu.

Blok wejścia/wyjścia (IOB) XC2S200-5FG256I

Wewnętrzna struktura bloków we/wy łączy zewnętrzne piny pakietu z programowalną strukturą logiczną poprzez konfigurowalne ścieżki wejściowe i wyjściowe.Dane wyjściowe przechodzą przez przerzutnik oznaczony jako WYŁĄCZONY z kontrolą zegara i włączania, po którym następuje programowalny bufor wyjściowy, który steruje zewnętrznym pinem podczas pracy z zasilacza VCCO powiązanego z bankiem I O.Sygnały wejściowe z pinów pakietu przechodzą przez programowalny bufor wejściowy i opcjonalny programowalny stopień opóźnienia, zanim dotrą do wejściowego przerzutnika oznaczonego IFF, który synchronizuje sygnał z wewnętrznym zegarem.Dodatkowe elementy sterujące obejmują kontrolę trójstanową poprzez rejestr TFF, sygnały włączające zegar i wejścia resetowania, które zarządzają synchronizacją sygnału i kontrolą stanu.Programowalna sieć zabezpieczająca przed polaryzacją i ESD zabezpiecza interfejs pinów, podczas gdy wewnętrzne połączenia odniesienia i połączenia VREF obsługują standardy we/wy odniesienia napięcia, wspólne dla całego banku.

Zastosowania XC2S200-5FG256I

Cyfrowe systemy trasowania sygnału

Programowalne zasoby logiczne umożliwiają urządzeniu zarządzanie trasowaniem i przetwarzaniem sygnałów cyfrowych w sprzęcie komunikacyjnym.Jego konfigurowalne bloki logiczne mogą implementować niestandardowe ścieżki logiczne, które obsługują przesyłanie danych pomiędzy komponentami systemu, zachowując jednocześnie stabilne zachowanie taktowania.

Jednostki sterujące automatyki przemysłowej

Przemysłowe systemy sterowania często wymagają elastycznej logiki cyfrowej, którą można dostosować do różnych procesów maszynowych.Urządzenie może zarządzać sygnałami sterującymi, wejściami czujników i wyjściami siłowników, wspierając niezawodne działanie w zautomatyzowanych środowiskach produkcyjnych.

Wbudowane platformy prototypowania sprzętu

Platformy programistyczne często korzystają z programowalnych urządzeń logicznych do testowania projektów cyfrowych przed ostateczną produkcją sprzętu.Urządzenie umożliwia projektantom implementację i modyfikację struktur logicznych w trakcie rozwoju, umożliwiając efektywne testowanie cyfrowych funkcji sterujących.

Mostkowanie interfejsu komunikacyjnego

Systemy łączące wiele protokołów komunikacyjnych mogą wykorzystywać urządzenie do translacji lub trasowania sygnałów cyfrowych między interfejsami.Jego programowalna logika umożliwia tworzenie niestandardowych ścieżek danych łączących procesory, urządzenia pamięci i kontrolery komunikacyjne.

Samochodowe podsystemy elektroniczne

Elektroniczne jednostki sterujące w pojazdach wymagają programowalnej logiki do zarządzania sygnałami i koordynacji systemu.Urządzenie może obsługiwać cyfrowe zadania sterujące, interfejsy komunikacyjne i funkcje synchronizacji w elektronice samochodowej.

Logika sterowania elektronicznego użytkownika

Cyfrowe urządzenia konsumenckie często wymagają kompaktowej programowalnej logiki do zarządzania funkcjami systemu.Urządzenie może koordynować sygnały interfejsu użytkownika, kontrolować czas i komunikację wewnętrzną pomiędzy komponentami produktów elektronicznych.

XC2S200-5FG256I Zalety i wady

Zalety

• Programowalna struktura logiczna umożliwia rekonfigurację obwodów cyfrowych po instalacji

• W niektórych konstrukcjach zintegrowana pamięć blokowa umożliwia przechowywanie danych bez pamięci zewnętrznej

• Duża liczba pinów wejściowych i wyjściowych umożliwia elastyczną łączność systemu

• Stabilna praca w przemysłowych warunkach temperaturowych

• Kompaktowy pakiet BGA obsługuje gęste układy płytek drukowanych

• Wewnętrzne obwody dostrajania zegara pomagają zachować spójne zachowanie taktowania

Wady

• Pojemność logiczna jest mniejsza niż w nowszych urządzeniach programowalnych

• Rozmiar pamięci chipa jest ograniczony w porównaniu z nowoczesnymi rodzinami logiki programowalnej

• Zużycie energii może być wyższe niż w przypadku nowszych architektur niskonapięciowych

• Nie obejmuje zaawansowanych, zintegrowanych zasobów przetwarzania sygnału

• Wymaga zewnętrznej pamięci konfiguracyjnej do programowania urządzenia

Alternatywy dla XC2S200-5FG256I

| Numer części | Producent | Kluczowe funkcje | Użyj przypadku/notatek |

| XC2S200-5FGG256I | AMD | Spartan-II FPGA z konfigurowalnymi blokami logicznymi, rozproszoną pamięcią RAM i programowalnymi zasobami routingu.Działa przy napięciu rdzenia 2,5 V i zapewnia tysiące komórek logicznych do wdrażania niestandardowych obwodów cyfrowych. | Stosowany w wbudowanym przetwarzaniu, sterowaniu przemysłowym i sprzęcie komunikacyjnym, gdzie wymagana jest programowalna logika i niezawodne działanie w przemysłowych zakresach temperatur. |

| XC2S200-5FGG256C | AMD | Urządzenie FPGA z rodziny Spartan-II, które integruje programowalne elementy logiczne, bloki pamięci wewnętrznej i konfigurowalne połączenia we/wy w celu zapewnienia elastycznego projektowania cyfrowego. | Nadaje się do elektroniki użytkowej, modułów komunikacyjnych i platform prototypowych, gdzie wymagana jest umiarkowana gęstość logiczna i elastyczna konfiguracja sprzętowa. |

| XC2S200-5FG256C | AMD | Programowalne urządzenie FPGA oferujące konfigurowalne komórki logiczne, zasoby pamięci wewnętrznej i wiele konfigurowalnych przez użytkownika pinów we/wy w celu implementacji złożonych obwodów cyfrowych w jednym chipie. | Stosowane w systemach akwizycji danych, platformach przetwarzania sygnałów i projektach wbudowanych, które wymagają programowalnego sprzętu cyfrowego. |

| XC2S200-5FGG456I | AMD | Układ FPGA Spartan-II o dużej liczbie pinów, zapewniający programowalne bloki logiczne, wbudowaną pamięć i dużą liczbę połączeń we/wy dla złożonych systemów cyfrowych. | Stosowany w automatyce przemysłowej, zaawansowanym sprzęcie komunikacyjnym i systemach wbudowanych o dużej liczbie wejść/wyjść wymagających elastycznej programowalnej logiki i rozszerzonej obsługi temperaturowej. |

O AMD Xilinx

AMD Xilinx to firma zajmująca się technologią półprzewodników, znana z opracowywania programowalnych urządzeń logicznych i adaptacyjnych platform obliczeniowych.Firma powstała jako Xilinx, a później stała się częścią Advanced Micro Devices.Jej prace skupiają się na programowalnych macierzach bramek, systemach adaptacyjnych na urządzeniach chipowych oraz programowalnych platformach akceleracyjnych stosowanych w informatyce, komunikacji, elektronice samochodowej i systemach przemysłowych.Firma od kilkudziesięciu lat opracowuje programowalne architektury logiczne, wspierając projektowanie sprzętu cyfrowego za pomocą konfigurowalnych urządzeń, które umożliwiają definiowanie obwodów po wyprodukowaniu.Jej produkty są szeroko stosowane w systemach wbudowanych, infrastrukturze sieciowej, sprzęcie do przetwarzania sygnałów i elektronicznych systemach sterowania.

Wniosek

Układ FPGA XC2S200-5FG256I zapewnia elastyczny sposób budowania logiki cyfrowej bezpośrednio w sprzęcie.Można skonfigurować jego bloki logiczne, zasoby pamięci oraz połączenia wejściowe i wyjściowe, aby obsługiwały różne zadania systemowe.Jego wewnętrzna struktura umożliwia kierowanie sygnału, kontrolę taktowania i przechowywanie danych w jednym programowalnym urządzeniu.Dzięki konfigurowalnemu zrozumieniu architektury i architektury aplikacji XC2S200-5FG256I FPGA, urządzenie może obsługiwać wbudowaną elektronikę, interfejsy komunikacyjne i systemy sterowania.Zrozumienie jego układu, funkcji i zastosowań pomoże Ci zobaczyć, w jaki sposób programowalne urządzenia logiczne obsługują nowoczesny sprzęt cyfrowy.Ułatwia to ocenę, czy XC2S200-5FG256I pasuje do potrzeb Twojego projektu elektronicznego.

Arkusz danych w formacie PDF

Karta katalogowa XC2S200-5FG256I:

O nas

ALLELCO LIMITED

Czytaj więcej

Szybkie zapytanie.

Proszę wysłać zapytanie, natychmiast odpowiemy.

Często Zadawane Pytania [FAQ]

1. Jakim typem urządzenia jest XC2S200-5FG256I

XC2S200-5FG256I to programowalna macierz bramek.To jest programowalne urządzenie logiczne umożliwiające konfigurację obwodów cyfrowych poprzez oprogramowanie, a nie stałą konstrukcję sprzętu.

2. Ile pinów wejściowych i wyjściowych zapewnia XC2S200-5FG256I

Urządzenie XC2S200-5FG256I obsługuje do 176 wejść konfigurowalnych przez użytkownika i piny wyjściowe, umożliwiające połączenie z wieloma komponentami zewnętrznymi i interfejsy komunikacyjne.

3. Do czego służy blokowa pamięć RAM w układzie FPGA XC2S200

Block RAM zapewnia pamięć wewnętrzną służącą do tymczasowego przechowywania danych, buforowanie, tabele przeglądowe i inne zadania związane z obsługą danych w ramach programowalny układ logiczny.

4. Gdzie jest powszechnie używany XC2S200-5FG256I

To urządzenie jest często używane w elektronice wbudowanej, komunikacji systemy automatyki przemysłowej i cyfrowe systemy sterowania które wymagają programowalnej logiki sprzętowej.

5. Jakiego rodzaju opakowania używa XC2S200-5FG256I

XC2S200-5FG256I jest dostępny w formacie siatki składającej się z 256 kulek, co pozwala na dużą liczbę połączeń w kompaktowej obudowie nadaje się do gęstych układów płytek drukowanych.

Zrozumienie złączy DVI: wszystko, co musisz wiedzieć

na 2026/03/9

Przewodnik po chipie interfejsu ADM560JRS, funkcje i zastosowania

na 2026/03/5

Popularne posty

-

Złożone komputery zestawu instrukcji: Jak zmieniły obliczenia?

na 8000/04/18 147757

-

Pinout i funkcje USB-C

na 2000/04/18 111932

-

Korzystanie z prymitywnych symulacji XILINX: kompleksowy przewodnik po projekcie i symulacji FPGA

na 1600/04/18 111349

-

Napięcia zasilania w elektronice: znaczenie VCC, VDD, VEE, VSS i GND

na 0400/04/18 83719

-

RJ45 Podręcznik złącza: pinout, okablowanie, typy kablowe i zastosowania

na 1970/01/1 79508

-

Ostateczny przewodnik po kodach kolorów drutu w nowoczesnych systemach elektrycznych

Sposób, w jaki nasze systemy elektryczne używają kolorów, nie jest tylko dla wyglądu.Każdy kolor drutu wskazuje teraz określoną funkcję, ułatwiając poprawną identyfikację komponentów elektrycznych ...na 1970/01/1 66894

-

Jakość (Q) Współczynnik: Równania i zastosowania

Współczynnik jakości lub „Q” jest ważny podczas sprawdzania, jak dobrze induktory i rezonatory działają w systemach elektronicznych, które wykorzystują częstotliwości radiowe (RF).„Q” mierzy, jak d...na 1970/01/1 63010

-

Przewodnik zaworu oczyszczania: funkcja, objawy, testowanie i wymiana w celu optymalnej wydajności silnika

Zawór czyszczenia jest kluczową częścią systemu samochodu, który pomaga utrzymać w czystości powietrza poprzez zarządzanie oparami paliwowymi, zanim będą mogły uciec do atmosfery.To nie tylko pomag...na 1970/01/1 62996

-

Osiągnięcie wydajności szczytowej przy maksymalnym twierdzeniu o przeniesieniu mocy

Twierdzenie o maksymalnym przeniesieniu mocy wyjaśnia, w jaki sposób energia ze źródła, takiego jak akumulator lub generator, płynie do podłączonego obciążenia.Pokazuje dokładny warunek, w którym o...na 1970/01/1 54081

-

A23 Specyfikacje i kompatybilność baterii

Akumulator A23 to mała akumulator w kształcie cylindra o wysokim napięciu.Nazywany również 23a, 23E lub Mn21, działa przy 12 woltach i znacznie wyższy niż akumulatory AA lub AAA.Jego specj...na 1970/01/1 52113