LCMXO2280C-3TN100C FPGA: Funkcje, specyfikacje, aplikacje i arkusz danych

LCMXO2280C-3TN100C to kompaktowa, energooszczędna FPGA z serii Machxo Lattice Semiconductor, zaprojektowana do wypełnienia luki między CPLD i tradycyjnymi FPGA.Z 2280 lutami, wbudowaną pamięcią i wszechstronnymi opcjami we/wy, obsługuje szeroką gamę cyfrowych aplikacji logicznych, w tym logikę kleju, mostkowanie magistrali, sterowanie ulepszeniem i rozszerzenie we/wy.Niniejszy przewodnik bada jego funkcje, specyfikacje, architekturę bloków, modele CAD, etapy programowania i zalety, zapewniając kompleksowe odniesienie do integracji z twoimi projektami.Katalog

Przegląd LCMXO2280C-3TN100C

. LCMXO2280C-3TN100C Z serii Machxo Lattice Semiconductor znajduje się progatowo programowalna tablica bramy (FPGA), która łączy cechy CPLD i tradycyjne FPGA w wszechstronne i wydajne rozwiązanie jednoręczne.To urządzenie oferuje 2280 tabel wyszukiwania (LUTS), umożliwiając złożone funkcje logiczne i zarządzanie danymi, w połączeniu z 28 262 bitami wbudowanego bloku RAM dla solidnego przechowywania i buforowania danych.Zaprojektowany pod kątem elastyczności, ma 73 programowalne kołki we/wy i działa na przyjaznym zasięgu zakresu napięcia od 1,71 V do 3,465 V.Oczekiwany w kompaktowym 100-pinowym cienkim quad płaskim (TQFP) o wymiarach zaledwie 14 x 14 mm, LCMXO2280C-3TN100C jest idealny do zastosowań ograniczonych przestrzeni.Działa w komercyjnym zakresie temperatur od 0 ° C do 85 ° C, zapewniając niezawodność w różnych warunkach środowiskowych.Ta FPGA jest dostosowana do zastosowań takich jak logika kleju, mostowanie magistrali, kontrola ulepszenia i ogólna logika kontroli, oferująca wysokie bezpieczeństwo i natychmiastowe funkcje, które są charakterystycznymi cechami CPLDS.Lattice's Isplever® Design Tools dodatkowo usprawnia proces implementacji, bezproblemowo integrując się z popularnymi narzędziami do syntezy logicznej w celu optymalizacji umieszczenia i routingu projektowania.Ta kompatybilność syntezy zapewnia, że LCMXO2280C-3TN100C może zaspokoić rygorystyczne wymagania złożonych, wysokowydajnych zastosowań.

Jeśli szukasz niezawodnych, wysokowydajnych FPGA, kupowanie luzem LCMXO2280C-3TN100C jest inteligentnym wyborem.

Modele CAD LCMXO2280C-3TN100C

Symbol LCMXO2280C-3TN100C

LCMXO2280C-3TN100C STOPRINT

Model 3D LCMXO2280C-3TN100C

Funkcje LCMXO2280C-3TN100C

• • Nielatywne, nieskończenie rekonfigurowalne: LCMXO2280C-3TN100C jest zaprojektowany z pamięcią nieulotną, co pozwala jej natychmiastowo zasilać bez potrzeby zewnętrznej pamięci konfiguracji.Ta funkcja zwiększa bezpieczeństwo projektu i upraszcza ogólną architekturę systemu, eliminując potrzebę osobnej pamięci konfiguracji, jednocześnie umożliwiając nieskończoną rekonfigurację.

• • Wysoka gęstość I/Wy do gęstości logicznej: To urządzenie integruje 2280 LUT4S (tabele wyszukiwania), które mogą wykonywać złożone operacje logiczne, oraz 73 programowalne piny we/wy, które ułatwiają rozległe opcje interfejsu.Wysoki stosunek I/O do logiki sprawia, że ta FPGA jest idealna do zastosowań zorientowanych na interfejsy, zapewniając dużą elastyczność dla różnych wymagań projektowych.

• • Wbudowana i rozproszona pamięć: LCMXO2280C-3TN100C zawiera 28 262 bitów wbudowanego bloku RAM i do 7,5 kbit rozproszonego pamięci RAM.Ta kombinacja typów pamięci oferuje wydajne, skalowalne rozwiązania do przechowywania danych i zarządzania danymi na chipie, obsługujące szeroki zakres aplikacji, od prostego buforowania danych po złożone maszyny stanowe.

• • Elastyczny bufor we/wy : Wyposażony w programowalne bufory Sysio ™, FPGA obsługuje różne standardy interfejsu, w tym LVCMOS i LVTTL.Ta elastyczność zapewnia kompatybilność z szeroką gamą istniejących i powstających cyfrowych standardów logicznych, umożliwiając spełnienie określonych wymagań interfejsu bez dodatkowych komponentów.

• • Sysclock ™ PLLS: Wyposażony w maksymalnie dwie analogiczne pętle blokowane w fazie (PLL), FPGA może wykonywać zadania zarządzania zegara, takie jak mnożenie, podział i przesuwanie fazy.Ta zdolność jest ważna dla projektowania systemów, które wymagają precyzyjnych korekt czasu zegara, aby spełnić rygorystyczne wymagania synchronizacji i czasowe.

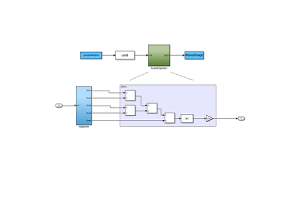

Schemat blokowy LCMXO2280C-3TN100C

Schemat PFU

. Schemat blokowy LCMXO2280C-3TN100C pokazuje, w jaki sposób układ przetwarza funkcje logiczne.Koncentruje się na Programowalny jednostka funkcyjna (PFU), który składa się z mniejszych części zwanych plasterkami.Każdy kawałek ma Tabele wyszukiwania (Luts) z logiką noszenia i flip-flops (FFS) lub zatrzaski.. Lut4 i przewożą bloki Wykonaj proste operacje matematyczne i logiczne, podczas gdy flip-flops/zatrzaski przechowują dane tymczasowe.Sygnały Wprowadź PFU z systemu routingu, który łączy różne bloki logiczne wewnątrz układu.Pierwszy kawałek otrzymuje dane wejściowe FCIN (Funkcja przenieś wejście), a sygnał przesuwa się przez plastry krok po kroku.Łańcuch przeniesienia pomaga przyspieszyć operacje arytmetyczne, szybko przekazując wartości z jednego kawałka do drugiego.Ostateczny wynik pojawia się Fco (Funkcja przenieś wyjście).Na dole każdego plastra sygnały wracają do systemu routingu w celu dalszego użycia.Ta konfiguracja ułatwia projektowanie i łączenie różnych funkcji logicznych w FPGA.

Schemat plastra

. Schemat wycinka LCMXO2280C-3TN100C pokazuje, w jaki sposób niewielka część FPGA przetwarza logikę i zadania arytmetyczne.Każdy kawałek ma dwa LUT4 i noszenie bloki, które są jak małe kalkulatory, które przestrzegają ustalonych reguł, aby przetwarzać sygnały wejściowe.Bloki te pobierają sygnały z systemu routingu i wykonują operacje, takie jak dodanie lub inne funkcje logiczne.Każdy Lut Uzyskuje dane wejściowe (A, B, C, D) i decyduje, jakie wyjście powinno wytworzyć.A LUT Expansion Mux Pomaga połączyć dwa lut, gdy potrzebna jest bardziej złożona funkcja.Wyniki (F, suma, OFX0, OFX1) można przechowywać w klapkach (FFS) lub zatrzaskach, które przechowują dane do późniejszego użycia.Istnieją sygnały kontrolne, takie jak Zegar (CLK) do operacji czasowych, Zegar włącza (Ce) w celu włączenia lub wyłączania procesów oraz Nastawić (LSR) Aby w razie potrzeby wyczyścić przechowywane dane.Slice łączy się z innymi plasterkami i systemem routingu, umożliwiając płynne poruszanie się sygnałów w FPGA.Ta konstrukcja ułatwia efektywne tworzenie zarówno prostych, jak i złożonych obwodów cyfrowych.

Specyfikacje LCMXO2280C-3TN100C

|

Typ |

Parametr |

|

Producent |

Lattice Semiconductor Corporation |

|

Szereg |

Machxo |

|

Opakowanie |

Taca |

|

Status części |

Aktywny |

|

Liczba laboratoriów/CLB |

285 |

|

Liczba elementów/komórek logicznych |

2280 |

|

Całkowite bity RAM |

28262 |

|

Liczba we/wy |

73 |

|

Napięcie - zasilanie |

1,71 V ~ 3,465 V. |

|

Typ montażu |

Mocowanie powierzchniowe |

|

Temperatura robocza |

0 ° C ~ 85 ° C (TJ) |

|

Pakiet / obudowa |

100-lqfp |

|

Pakiet urządzeń dostawcy |

100-TQFP (14x14) |

|

Podstawowy numer produktu |

LCMXO2280 |

Aplikacje LCMXO2280C-3TN100C

Logika kleju

LCMXO2280C-3TN100C FPGA wyróżnia się jako logika kleju w systemach elektronicznych.Logika kleju służy przede wszystkim do zintegrowania różnych dyskretnych komponentów w systemie, umożliwiając im efektywną komunikację lub działanie.Ta FPGA może wdrażać wiele funkcji logicznych, które w przeciwnym razie mogłyby wymagać kilku różnych rodzajów układów, upraszczając projektowanie i poprawę wydajności poprzez zmniejszone opóźnienie sygnału i niższe wymagania dotyczące przestrzeni płyty.

Mostkowanie autobusów i interfejs

Ta FPGA jest również biegła przy mostowaniu i interfejsie magistrali, która obejmuje połączenie dwóch różnych protokołów magistrali lub dostosowywanie poziomów sygnału między nimi.Zapewnia płynne przesyłanie danych i kompatybilność komunikacji w różnych komponentach poprzez tłumaczenie formatów danych, poziomów napięcia lub charakterystyk czasu.Ta aplikacja jest wykorzystywana w systemach, w których nowsza technologia musi łączyć się ze starszymi systemami lub gdzie różne podsystemy działają zgodnie z różnymi standardami.

Kontrola ulepszenia

W aplikacjach sterowania uruchomieniem LCMXO2280C-3TN100C zarządza sekwencją inicjalizacji systemów elektronicznych.Ta FPGA może zorganizować kolejność, w której różne komponenty systemowe są aktywowane podczas fazy uruchamiania, aby zapobiec uszkodzeniom i zapewnić funkcjonalność.Jest zaprogramowany do obsługi zadań, takich jak włączanie lub wyłączanie mocy dla określonych komponentów w dokładnym czasie, monitorowanie statusu systemu i upewnienie się, że wszystkie części działają przed przejściem do pełnej aktywacji systemu.

Rozszerzenie we/wy ogólnego zastosowania

FPGA służy jako doskonałe rozwiązanie do rozszerzenia we/wy ogólnego zastosowania.Może zapewnić dodatkowe interfejsy wejściowe/wyjściowe dla systemów, które wymagają większej liczby pinów we/wy niż oferują ich główne procesory.Jest to przydatne w złożonych systemach, które muszą obsługiwać dużą liczbę wejść i wyjść, takich jak systemy kontroli przemysłowej, zaawansowana elektronika lub urządzenia komunikacyjne.

Mostkowanie interfejsu

LCMXO2280C-3TN100C jest używany do mostowania interfejsu, gdzie pomaga łączyć różne interfejsy komunikacji w systemie.Ta aplikacja jest świetna do zapewnienia, że komponenty z niezgodnymi interfejsami mogą nadal skutecznie komunikować się.Na przykład może to tłumaczyć między protokołami SPI i I2C lub między szybkimi strumieniami danych szeregowych a równoległymi wejściami, zapewniając bezproblemowy przepływ danych i integrację systemu.

LCMXO2280C-3TN100C Podobne części

Kroki programowania LCMXO2280C-3TN100C

Programowanie FPGA LCMXO2280C-3TN100C to proces obejmujący kilka kroków.Oto prostszy przewodnik, który pomoże w zaprogramowaniu tego urządzenia za pomocą narzędzi dostarczanych przez Lattice Semiconductor.

1. Wejście do projektu

Pierwszy krok w programowaniu LCMXO2280C-3TN100C polega na tworzeniu projektu obwodu cyfrowego.Zazwyczaj odbywa się to za pomocą języka opisu sprzętu (HDL), takiego jak VHDL lub Verilog.Języki te pozwalają opisać strukturę i zachowanie obwodu cyfrowego w formie tekstowej.Wpis projektowy można wykonać przy użyciu dowolnego standardowego edytora HDL lub zintegrowanego środowiska programistycznego (IDE), które obsługuje te języki.Ważne jest, aby zapewnić, że kod HDL jest bezbłędny i wydajnie opisuje wymagane funkcje, ponieważ stanowi to podstawę implementacji FPGA.

2. Synteza

Po zakończeniu projektu HDL następnym krokiem jest synteza.Podczas tego procesu narzędzie do syntezy, takie jak te dostarczone przez dostawców sieci lub zewnętrznych, przekształca kod HDL w listę netto.Lista netto jest opisem obwodu pod względem wykresu węzłów reprezentujących bramy logiczne i krawędzi reprezentujące połączenia między tymi bramami.Ten krok obejmuje również optymalizację projektu w celu lepszej wydajności i minimalizację wykorzystania zasobów.Narzędzie do syntezy sprawdza błędy logiczne i zapewnia, że projekt spełnia wymagania dotyczące pomiaru czasu.Udana synteza jest weryfikowana poprzez symulację, która testuje projekt w różnych warunkach, aby upewnić się, że zachowuje się zgodnie z oczekiwaniami.

3. Umieść i trasę

Po syntezie rozpoczyna się proces miejsca i trasy.Ten etap obejmuje mapowanie zsyntetyzowanej listy netto na faktyczną architekturę FPGA.Obejmuje umieszczenie elementów logicznych w fizycznych blokach FPGA i połączenia routingu między nimi.Narzędzia projektowe Lattice, zaprojektowane dla FPGA, oferują zautomatyzowane możliwości miejsca i trasy, ale możesz również dokonywać ręcznych korekt w celu optymalizacji wydajności i wykorzystania zasobów.Ten krok jest ważny, ponieważ wpływa bezpośrednio na szybkość, wydajność i zużycie energii produktu końcowego.

4. Generowanie plików programowania

Po procesie miejsca i trasy następnym krokiem jest wygenerowanie pliku programowania.Ten plik zawiera dane konfiguracyjne potrzebne do zaprogramowania FPGA.Przekłada informacje o umieszczaniu i routingu na format, który FPGA może zrozumieć i użyć do skonfigurowania wewnętrznych bloków logicznych i ścieżek routingu.Plik programowania ma rozszerzenie, takie jak .JED lub .bit, w zależności od FPGA i użytych narzędzi.

5. Programowanie urządzeń

Ostatnim krokiem jest załadowanie pliku programowania do FPGA LCMXO2280C-3TN100C.Można to zrobić za pomocą programatora sprzętowego kompatybilnego z urządzeniem, takim jak programista JTAG.Programator łączy się z FPGA za pomocą standardowego połączenia i przenosi dane zawarte w pliku programowania do pamięci nieulotnej FPGA lub tymczasowej pamięci konfiguracji, w zależności od konfiguracji.Po zaprogramowaniu FPGA zacznie funkcjonować zgodnie ze specyfikacjami projektowymi określonymi w kodzie HDL.

LCMXO2280C-3TN100C Zalety

Możliwości natychmiastowe

FPGA LCMXO2280C-3TN100C wyróżnia się z możliwością „instant-on”, przede wszystkim ze względu na nieulotną architekturę.W przeciwieństwie do tradycyjnych FPGA, które zależą od zewnętrznych wspomnień konfiguracyjnych i trwają dłuższe czasy rozruchu, ta FPGA jest natychmiastowa, gdy tylko zastosowano zasilanie.Funkcja natychmiastowa nie tylko upraszcza projekt systemu, eliminując potrzebę przechowywania konfiguracji zewnętrznej, ale także zwiększa niezawodność i bezpieczeństwo poprzez zmniejszenie potencjalnych punktów awarii i ekspozycji na uszkodzenie konfiguracji.

Operacja o niskiej mocy

Efektywność energetyczna jest kolejną zaletą FPGA LCMXO2280C-3TN100C, charakteryzującego się niskim zużyciem energii i innowacyjnym trybem uśpienia.Ten tryb dramatycznie zmniejsza wymagania dotyczące mocy FPGA, gdy nieaktywne, co jest dobre w przedłużeniu żywotności baterii w urządzeniach przenośnych lub zmniejszaniu kosztów energii w na dużą skalę.Zastosowania takie jak technologia noszenia, urządzenia do zdalnego wykrywania i świadoma środowiskowa elektronika konsumpcyjna w dużej mierze korzystają z tych funkcji, ponieważ wymagają one urządzeń, które mogą zachować funkcjonalność, jednocześnie zarządzając zużycie energii w celu zapewnienia długowieczności i zrównoważonego rozwoju.

Wysoka integracja z wbudowanymi funkcjami

LCMXO2280C-3TN100C jest wysoce zintegrowany, zawierający wbudowane bloki pamięci, wszechstronne obsługę we/wy i wbudowane pętle blokowane w fazie (PLLS).Ta integracja ułatwia zmniejszenie ogólnej liczby komponentów w systemach elektronicznych, co prowadzi do bardziej usprawnionych i opłacalnych projektów.Ten poziom integracji jest korzystny w aplikacjach wymagających gęstych, wysokiej funkcji urządzeń, takich jak inteligentna elektronika, zaawansowane systemy komunikacyjne i wyrafinowane sterowanie samochodowymi.

Wymiary opakowania LCMXO2280C-3TN100C

LCMXO2280C-3TN100C to Machxo FPGA z półprzewodnika Lattice, umieszczonego w pakiecie TQFP-100.Poniżej znajdują się wymiary opakowań dla 100-pin TQFP (pakiet Think Quad Flat):

|

Parametr |

Min (mm) |

Nom (mm) |

Max (mm) |

|

Rozmiar ciała (L × W) |

14 |

14 |

14 |

|

Grubość ciała |

1 |

- |

1.2 |

|

Pin |

0,5 |

0,5 |

0,5 |

|

Długość ołowiu |

0,45 |

0,6 |

0,75 |

|

Szerokość ołowiu |

0,17 |

0,22 |

0,27 |

|

Ołów koplanarium |

- |

- |

0,08 |

LCMXO2280C-3TN100C Producent

LCMXO2280C-3TN100C jest wytwarzany przez Lattice Semiconductor Corporation , wiodący dostawca programowalnych urządzeń logicznych o niskiej mocy.Lattice specjalizuje się w FPGA, CPLDS i innych programowalnych roztworach logicznych zoptymalizowanych pod kątem niskiego zużycia energii, czynników małej postaci i wydajności kosztowej.Seria Machxo, która obejmuje LCMXO2280C-3TN100C, jest zaprojektowana do aplikacji takich jak kontrola systemu, rozszerzenie we/wy i mostkowanie interfejsu.Lattice znana jest z technologii TRANSFR ™, umożliwiając programowalność w systemie i zdalne ulepszenia pola.Sieci półprzewodnikowy z siedzibą w Hillsboro w stanie Oregon zapewnia roztwory półprzewodnikowe dla aplikacji przemysłowych, motoryzacyjnych i komunikacyjnych, wzmacniając swoją reputację kluczowego gracza w programowalnym branży logicznej.

Wniosek

LCMXO2280C-3TN100C jest idealnym rozwiązaniem dla aplikacji wymagających nieulotnego, natychmiastowego FPGA o niskiej mocy z elastycznymi zasobami I/O i pamięci.Jego wysoka integracja, wydajność energetyczna i łatwość programowania sprawiają, że jest to wyjątkowy wybór do wbudowanej kontroli, interfejsu systemu i automatyzacji przemysłowej.Niezależnie od tego, czy jest używany do sekwencjonowania uruchamiania, mostkowania protokołu, czy ogólnej logiki sterowania, ta FPGA zapewnia niezawodną wydajność w środowiskach ograniczonych kosmicznych.Wykorzystując narzędzia Isplever Lattice, możesz skutecznie wdrażać złożoną logikę cyfrową z zoptymalizowaną wydajnością i minimalnym czasem rozwoju.

Arkusz danych pdf

LCMXO2280C-3TN100C Arkusze danych:

O nas

ALLELCO LIMITED

Czytaj więcej

Szybkie zapytanie.

Proszę wysłać zapytanie, natychmiast odpowiemy.

Często Zadawane Pytania [FAQ]

1. Czy LCMXO2280C-3TN100C jest odpowiedni do zastosowań operowanych baterią o niskiej mocy?

Tak.LCMXO2280C-3TN100C jest zoptymalizowany pod kątem niskiego zużycia energii z zaawansowanym trybem uśpienia, umożliwiając wydajne działanie w systemach zasilanych baterią, takimi jak urządzenia IoT, urządzenia do noszenia i instrumenty ręczne.Jego funkcja natychmiastowa zapewnia minimalne opóźnienia w ulepszeniu, dalsze oszczędzanie energii.

2. Czy LCMXO2280C-3TN100C można zaprogramować wiele razy?

Tak, ta FPGA obsługuje nieskończoną rekonfigurację, co oznacza, że możesz aktualizować projekt logiki tak często, jak to konieczne.W przeciwieństwie do jednorazowych urządzeń programowalnych, ta funkcja pozwala na elastyczność projektowania i łatwe debugowanie.Zachowuje swoją konfigurację nawet po cyklu mocy, zapewniając niezawodne działanie w systemach krytycznych misji.

3. Czy mogę wymienić inne CPLD lub FPGA LCMXO2280C-3TN100C?

Tak, ta FPGA służy jako doskonała wymiana wielu CPLD i FPGA o niskiej gęstości ze względu na jego możliwości natychmiastowe, pamięć wbudowaną i elastyczną obsługę we/wy.Może zastąpić urządzenia Altera Max, Xilinx Coolrunner i Microsemi igloo w różnych aplikacjach.

4. Czy LCMXO2280C-3TN100C obsługuje zdalne aktualizacje oprogramowania układowego?

Tak, za pomocą technologii Transfr ™ Lattice, możesz wykonywać zdalne aktualizacje pola bez zakłócania funkcjonalności systemu.Ta funkcja jest bardzo korzystna w aplikacjach przemysłowych i osadzonych, w których należy zastosować aktualizacje oprogramowania układowego bez wyłączenia całego systemu.

5. Jakie narzędzia do programowania są wymagane dla LCMXO2280C-3TN100C?

Aby zaprogramować LCMXO2280C-3TN100C, potrzebujesz oprogramowania Diamond Lattice lub Isplever wraz z kompatybilnym programistą, takim jak Lattice HW-USBN-2B lub standardowy interfejs JTAG.Narzędzia te zapewniają pełne wsparcie dla syntezy projektowania, symulacji i debugowania sprzętu.

Wzmacniacze mocy RF: jak działają, który typ jest bardziej wydajny

na 2025/03/18

Zrozumienie bezpośredniego i pośredniego rozkładu dla komponentów elektronicznych

na 2025/03/18

Popularne posty

-

Złożone komputery zestawu instrukcji: Jak zmieniły obliczenia?

na 8000/04/18 147758

-

Pinout i funkcje USB-C

na 2000/04/18 111958

-

Korzystanie z prymitywnych symulacji XILINX: kompleksowy przewodnik po projekcie i symulacji FPGA

na 1600/04/18 111349

-

Napięcia zasilania w elektronice: znaczenie VCC, VDD, VEE, VSS i GND

na 0400/04/18 83725

-

RJ45 Podręcznik złącza: pinout, okablowanie, typy kablowe i zastosowania

na 1970/01/1 79510

-

Ostateczny przewodnik po kodach kolorów drutu w nowoczesnych systemach elektrycznych

Sposób, w jaki nasze systemy elektryczne używają kolorów, nie jest tylko dla wyglądu.Każdy kolor drutu wskazuje teraz określoną funkcję, ułatwiając poprawną identyfikację komponentów elektrycznych ...na 1970/01/1 66924

-

Przewodnik zaworu oczyszczania: funkcja, objawy, testowanie i wymiana w celu optymalnej wydajności silnika

Zawór czyszczenia jest kluczową częścią systemu samochodu, który pomaga utrzymać w czystości powietrza poprzez zarządzanie oparami paliwowymi, zanim będą mogły uciec do atmosfery.To nie tylko pomag...na 1970/01/1 63078

-

Jakość (Q) Współczynnik: Równania i zastosowania

Współczynnik jakości lub „Q” jest ważny podczas sprawdzania, jak dobrze induktory i rezonatory działają w systemach elektronicznych, które wykorzystują częstotliwości radiowe (RF).„Q” mierzy, jak d...na 1970/01/1 63017

-

Osiągnięcie wydajności szczytowej przy maksymalnym twierdzeniu o przeniesieniu mocy

Twierdzenie o maksymalnym przeniesieniu mocy wyjaśnia, w jaki sposób energia ze źródła, takiego jak akumulator lub generator, płynie do podłączonego obciążenia.Pokazuje dokładny warunek, w którym o...na 1970/01/1 54086

-

A23 Specyfikacje i kompatybilność baterii

Akumulator A23 to mała akumulator w kształcie cylindra o wysokim napięciu.Nazywany również 23a, 23E lub Mn21, działa przy 12 woltach i znacznie wyższy niż akumulatory AA lub AAA.Jego specj...na 1970/01/1 52153