EPM7256SQC208-10 Przewodnik: Funkcje, pinout, programowanie, aplikacje i arkusz danych

Ten przewodnik dotyczy EPM7256SQC208-10, rodzaju programowalnego układu wykonanego przez Intela (pierwotnie przez Altera).Pochodzi z rodziny Max® 7000s i jest znany z tego, że jest szybki, niezawodny i łatwy do zaprogramowania, gdy jest już w urządzeniu.W tym artykule wyjaśnia, co robi układ, jak to działa, gdzie jest używany i dlaczego jest to świetny wybór, jeśli potrzebujesz silnego i elastycznego urządzenia logicznego do swojego projektu.Katalog

EPM7256SQC208-10 Przegląd

. EPM7256SQC208-10 jest częścią rodziny Intela (wcześniej Altera) Max® 7000s, wysokowydajnego zakresu CPLD, znanego z solidnej programowania i optymalizacji logiki.Ten model oferuje około 5000 użytecznych bram i obejmuje 256 makrokomórków, umieszczonych w 208-pinowym plastikowym quadowym opakowaniu (PQFP).Działa z częstotliwością do 128,2 MHz i obsługuje napięcie robocze 5,0 V, z maksymalnym opóźnieniem propagacji 7,5 ns i sufitem temperatury operacyjnej +70 ° C.Kluczową cechą jest programowalność w systemie za pośrednictwem wbudowanego IEEE STD.1149.1 interfejs JTAG, umożliwiając konfigurację dynamiczną.Urządzenia Max® 7000S są wytwarzane przy użyciu zaawansowanej technologii CMOS, oferując takie funkcje, jak opóźnienia logiczne typu pin-to-pin tak szybkie jak 5 ns i częstotliwości kontrataków do 175,4 MHz.Rodzina przedstawia różnorodne opcje pakietów i jest zaprojektowana z programowalnymi klapkami makrokomórkami, które przyczyniają się do znacznych oszczędności energii w niektórych przypadkach ponad 50% redukcji.Ponadto zawiera bit bezpieczeństwa w zakresie ochrony zastrzeżonych projektów.

Jeśli Twoja organizacja potrzebuje solidnego programowalnego rozwiązania logicznego, EPM7256SQC208-10 jest niezawodnym wyborem, więc skontaktuj się z nami już dziś, aby zabezpieczyć zamówienie zbiorcze.

Modele CAD EPM7256SQC208-10

Symbol EPM7256SQC208-10

EPM7256SQC208-10 Stopprint

Model 3D EPM7256SQC208-10

Funkcje EPM7256SQC208-10

• • Wysoka gęstość logiczna: EPM7256SQC208-10 zapewnia około 5000 użytecznych bramek i zawiera 256 makrokomórków.Ta wysoka pojemność logiczna sprawia, że idealnie nadaje się do wdrażania złożonych obwodów kombinacyjnych i wydajnej integracji logicznej w kompaktowych projektach.

• • Szybka wydajność: Przy maksymalnej częstotliwości roboczej 128,2 MHz i opóźnieniu propagacji wynoszącym zaledwie 7,5 ns, ten CPLD zapewnia szybkie czasy przetwarzania i szybkiego reakcji, dobre dla zastosowań o dużej prędkości.

• • Programowalność w systemie (ISP): Wyposażony w IEEE STD.1149.1 interfejs JTAG, urządzenie umożliwia programowanie i testowanie systemu bez potrzeby usuwania fizycznego, ułatwiania iteracyjnego rozwoju i aktualizacji.

• • Zaawansowana architektura: Korzystając z Max Architektura drugiej generacji Altera i wyprodukowana z zaawansowaną technologią CMOS, EPM7256SQC208-10 oferuje zwiększoną wydajność i trwałość, zapewniając niezawodność w różnych środowiskach operacyjnych.

• • Zarządzanie energią: Urządzenie ma programowalne tryby oszczędzania energii, które mogą zmniejszyć zużycie energii o ponad 50% na makrokomórki, obsługując energooszczędne projekty i przedłużając żywotność baterii w zastosowaniach przenośnych.

• • Funkcje bezpieczeństwa: Programowalny bit bezpieczeństwa zapewnia ochronę przed nieautoryzowanym dostępem i kopiowaniem zastrzeżonych projektów, skutecznie chroniąc własność intelektualną.

• • Szerokie warunki pracy: Działając na poziomie 5,0 V i zdolne do funkcjonowania w temperaturach do +70 ° C, ten CPLD dostosowuje się do różnych warunków środowiskowych, dzięki czemu nadaje się zarówno do zastosowań przemysłowych, jak i komercyjnych.

• • Elastyczne standardy we/wy : Obsługuje operacje interfejsu I/O Multivolt ™, kompatybilne z systemami 3,3 V i 5.0 V.Ta elastyczność umożliwia bezproblemową integrację z istniejącym i nowym sprzętem, zmniejszając złożoność systemu i koszty.

• • Wsparcie projektowe: EPM7256SQC208-10 jest wspierany przez szereg narzędzi projektowych i opcji programowania, upraszczając proces rozwoju i umożliwiając skupienie się na innowacjach, a nie na problemy związane z kompatybilnością.

Schemat pinout EPM7256SQC208-10

Ten schemat pokazuje układ pinu dla układu EPM7256SQC208-10 z Altera.Chip ma 208 pinów, ułożonych ze wszystkich czterech stron w kwadratowym kształcie.Pin 1 zaczyna się w lewym górnym rogu, a liczby krążą wokół układu w kierunku przeciwnym do ruchu wskazówek zegara, w dół po lewej stronie do szpilki 53, przez dolne do pinu 105, po prawej stronie do pinu 157 i z powrotem do prawej górnej części.Etykiety pomagają wiedzieć, od czego zacząć i jak prawidłowo umieścić układ na płytce obwodowej.Nazwa w centrum „EPM7256E / EPM7256S” oznacza, że ten układ działa dla obu wersji Chip.Ten schemat jest ważny przy łączeniu mocy, sygnałów lub linii programowania z układem.

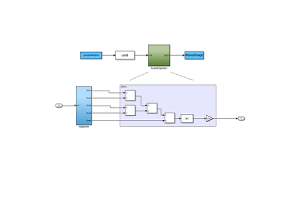

Schemat blokowy EPM7256SQC208-10

Schemat blokowy EPM7256SQC208-10 pokazuje, w jaki sposób układ jest zorganizowany do obsługi cyfrowych zadań logicznych.Ma cztery główne bloki logiczne o nazwie Lab A, B, C i D. Każdy blok zawiera 16 makrokomórków, które są podstawowymi częściami budowlanymi, które wykonują logikę.W sumie wewnątrz układu znajduje się 64 makrokomórki.Wokół tych bloków logicznych znajdują się bloki sterujące we/wy, które łączą układ do świata zewnętrznego poprzez piny wejściowe i wyjściowe.Każdy blok kontrolny zarządza 6 do 16 pinów, pozwalając sygnałom wejść lub wychodzić z układu w razie potrzeby.

W centrum znajduje się programowalna tablica połączeń (PIA), która działa jak system autostrady, pozwalając sygnałom przemieszczać się między blokami logicznymi i pinami we/wy.Umożliwia to kierowanie danych w dowolny sposób do projektu.W lewym górnym rogu schemat pokazuje pewne wejścia kontrolne, takie jak zegar globalny (GCLK), włączenie wyjściowe (OE) i Clear (GCLR).Sygnały te pomagają zarządzać czasem i zachowaniem obwodów logicznych na układie.

EPM7256SQC208-10 Specyfikacje

|

Typ |

Parametr |

|

Producent |

Altera/Intel |

|

Szereg |

Max® 7000s |

|

Opakowanie |

Taca |

|

Status części |

Przestarzały |

|

Typ programowalny |

W systemie programowalnym |

|

Czas opóźnienia TPD (1) Max |

10 ns |

|

Zasilanie napięcia - wewnętrzny |

4,75 V ~ 5,25 V. |

|

Liczba elementów/bloków logicznych |

16 |

|

Liczba makrokomórków |

256 |

|

Liczba bram |

5000 |

|

Liczba we/wy |

164 |

|

Temperatura robocza |

0 ° C ~ 70 ° C (TA) |

|

Typ montażu |

Mocowanie powierzchniowe |

|

Pakiet / obudowa |

208-BFQFP |

|

Pakiet urządzeń dostawcy |

208-PQFP (28x28) |

|

Podstawowy numer produktu |

EPM7256 |

Aplikacje EPM7256SQC208-10

Automatyzacja przemysłowa

EPM7256SQC208-10 jest szeroko stosowany w systemach automatyki przemysłowej.Jego wysoka gęstość logiczna i szybka wydajność umożliwiają złożone zadania kontrolne, płynnie łączą się z czujnikami i siłownikami.Ten CPLD jest idealny do zwiększania precyzji i wydajności w liniach produkcyjnych, systemach kontroli procesów i aplikacjach robotycznych.

Telekomunikacja

W telekomunikacji ten CPLD przoduje w zarządzaniu przepływem danych i integralności sygnału w różnych sieciach.Obsługuje funkcje takie jak konwersja sygnału, routing i przetwarzanie w przełącznikach i routerach, zapewniając solidną i wydajną infrastrukturę komunikacyjną.

Systemy motoryzacyjne

W branży motoryzacyjnej urządzenie to przyczynia się do niezawodności i wyrafinowania systemów, takich jak jednostki zarządzania silnikami, systemy informacyjno-rozrywkowe i technologie wspomagania kierowcy.Jego solidna wydajność w różnych warunkach sprawia, że nadaje się do zastosowań o kluczowym znaczeniu bezpieczeństwa.

Urządzenia medyczne

Precyzja i programowalność EPM7256SQC208-10 sprawiają, że jest cenny w sprzęcie medycznym, gdzie ważna jest dokładna kontrola i niezawodne działanie.Jest stosowany w urządzeniach do monitorowania witalnych pacjentów, zarządzania instrumentami diagnostycznymi i automatyzacji dostarczania leczenia.

Lotnisko i obrona

W lotnisku i obronie EPM7256SQC208-10 jest stosowany w systemach wymagających wysokiego poziomu niezawodności i wydajności, takich jak komunikacja satelitarna, pomoce nawigacyjne i kontrola sprzętu wojskowego.Jego zdolność do działania w ekstremalnych warunkach jest korzystna.

Instytucje edukacyjne i badawcze

Ten CPLD jest również popularny w warunkach edukacyjnych i projektach badawczych, w których przeprogramowanie i elastyczność ułatwiają eksperymenty i uczenie się w projektowaniu cyfrowym i elektronice.Umożliwia to prototypowanie i wydajne testowanie różnych projektów logicznych.

EPM7256SQC208-10 Podobne części

• • EPM7256ERC208-12

• • EPM7256SQC208-15

• • EPM7256EQC160-20

EPM7256SQC208-10 Kroki programowania

1. Wprowadź tryb ISP

Ten początkowy krok jest ważny, ponieważ przechodzi CPLD z trybu normalnego działania do trybu programowania systemu insystemu (ISP).Osiąga się to poprzez wysłanie określonego polecenia za pośrednictwem interfejsu JTAG.Podczas tego procesu wszystkie piny we/wy CPLD są TRI-STADE (wyłączone), aby uniknąć zakłóceń lub konfliktów z innymi składnikami obwodu.Przejście do trybu ISP przygotowuje urządzenie do bezpiecznego programowania i zajmuje około 1 milisekundy.

2. Sprawdź identyfikator

W trybie ISP system wykonuje kontrolę ID, aby upewnić się, że prawidłowe urządzenie jest programowane.Obejmuje to odczyt unikalny identyfikator krzemu urządzenia za pośrednictwem interfejsu JTAG.Ten krok jest dobry do sprawdzenia, czy polecenia i dane programowania zostaną wysłane do właściwego urządzenia, zapobiegając błędnym programowaniu i potencjalnym uszkodzeniu urządzenia.

3. Kasowanie masowe

Przed zaprogramowaniem nowych danych istniejące dane w CPLD muszą zostać usunięte.Krok kasowania masowego skutecznie usuwa wszystkie programowalne komórki w urządzeniu.Odbywa się to poprzez przesunięcie w instrukcji usuwania, a następnie zastosowanie 100-miliosekundowego impulsu, który usuwa cały układ.Ten krok jest ważny, aby upewnić się, że żadne pozostałości z poprzednich konfiguracji nie zakłócały nowego programowania.

4. Program

Ten krok obejmuje faktyczne programowanie CPLD, w którym nowe dane konfiguracyjne są zapisywane w urządzeniu.Dane i odpowiednie adresy są przesuwane na urządzenie przez interfejs JTAG.Każdy adres i para danych wymaga impulsu programowania, aby zapewnić prawidłowe zapisanie danych w nieulotnych komórkach pamięci CPLD.Ten krok jest powtarzany dla każdego punktu danych na mapie pamięci urządzenia.

5. Sprawdź

Po programowaniu należy sprawdzić, czy dane zostały poprawnie zapisane do urządzenia.Ten etap weryfikacji obejmuje odczytanie zaprogramowanych danych z każdego adresu i porównanie ich z oryginalnymi danymi wejściowymi.Ten krok zapewnia integralność danych i potwierdza, że proces programowania odniósł sukces bez żadnych błędów.

6. Wyjdź z trybu ISP

Ostatnim krokiem w procesie programowania jest wyjście z trybu ISP i zwrócenie CPLD do normalnego trybu operacyjnego.Odbywa się to poprzez wysłanie kolejnego polecenia za pośrednictwem interfejsu JTAG.Po udanym wyjściu piny we/wy są reaktywowane, a urządzenie wznawia normalną funkcję.Ten krok zwykle zajmuje również około 1 milisekundy.

EPM7256SQC208-10 Zalety

Konfiguracja nieulotna

EPM7256SQC208-10 wykorzystuje technologię EEPROM, pozwalając jej na stałe przechowywać swoją konfigurację.Ten nieulotny charakter oznacza, że urządzenie nie musi ponownie załadować swoich danych konfiguracyjnych z pamięci zewnętrznej za każdym razem, gdy jest włączany.Powoduje to szybsze czasy uruchamiania i zmniejsza ogólną złożoność projektu sprzętowego, eliminując potrzebę dodatkowych komponentów pamięci konfiguracji.

Programowalność w systemie (ISP)

Jedną z wyróżniających się funkcji EPM7256SQC208-10 jest obsługa programowalności w systemie.Umożliwia to programowanie i przeprogramowanie urządzenia podczas osadzenia w aplikacji końcowej bez konieczności fizycznego usunięcia.Ta funkcja upraszcza aktualizacje i modyfikacje, zapewniając elastyczność i łatwość użytkowania podczas rozwoju i przez cały cykl życia produktu.

Wysoka liczba we/wy i gęstość logiczna

Urządzenie oferuje znaczną liczbę zasobów logicznych i pinów we/wy, z 256 makrocekom i 164 pinami we/wy użytkowników.Ta wysoka liczba we/wy i gęstość logiczna umożliwiają integrację wielu funkcji z pojedynczym układem, ułatwiając bardziej złożone projekty, jednocześnie oszczędzając przestrzeń na PCB.Ta zaleta jest korzystna w aplikacjach, w których przestrzeń zarządu jest ważna, a wielofunkcyjność jest ważna.

Szybkie opóźnienie pin-pin

Z maksymalnym opóźnieniem pin-do pinu wynoszącym zaledwie 10 ns, EPM7256SQC208-10 może wykonywać szybkie operacje logiczne.Ten szybki czas reakcji jest świetny w aplikacjach wymagających szybkiego przetwarzania, takich jak szybka komunikacja lub obliczenia, zapewniając, że system spełnia rygorystyczne kryteria wydajności.

Kompatybilność z szerokim napięciem

EPM7256SQC208-10 został zaprojektowany tak, aby był elastyczny pod względem kompatybilności napięcia, obsługującą wewnętrzną obsługę na poziomie 5 V i I/O przy 3,3 V. Ta zdolność podwójnego napięcia umożliwia łatwą interfejs z systemami 3,3 V, jak i 5 V, zmniejszając potrzebę tłumaczy poziomu napięcia i uproszczenia projektowania systemu.

EPM7256SQC208-10 Wymiary pakowania

• • Typ pakietu: 208-BFQFP (plastikowy pakiet quad płaski)

• • Liczba szpilek: 208 przewodów

• • Rozmiar ciała (L × W): 28 mm × 28 mm

• • Styl montażowy: Technologia Mount Surface (SMT)

• • Pitek ołowiowy: Zazwyczaj 0,5 mm między pinami (standard dla BFQFP)

• • Materiał opakowania: Plastik

• • Grubość pakietu: Około 3,5 mm (nieznacznie różni się w zależności od producenta)

• • Charakterystyka termiczna: Brak odsłoniętego podkładki;Standardowe rozpraszanie otoczenia za pośrednictwem

• • Opakowanie tacki: Dostarczany w tace

EPM7256SQC208-10 Producent

EPM7256SQC208-10 został pierwotnie opracowany i wyprodukowany przez Altera Corporation, wiodący pionier w programowalnych urządzeniach logicznych znanych z serii CPLD MAX® 7000S.W 2015 r. Altera została przejęta przez Intel Corporation, jeden z największych na świecie producentów półprzewodników.Od czasu przejęcia Intel nadal wspiera i integruje technologie CPLD i FPGA Altera w ramach swojej grupy programowalnej rozwiązań.EPM7256SQC208-10 reprezentuje dziedzictwo Intela w oferowaniu wysokowydajnych, programowalnych rozwiązań logicznych dostosowanych do szerokiej gamy zastosowań przemysłowych, telekomunikacyjnych i osadzonych.Choć teraz sklasyfikowana jako przestarzała, część odzwierciedla długotrwały zaangażowanie Intela w niezawodne i elastyczne programowalne urządzenia logiczne.

Wniosek

EPM7256SQC208-10 to inteligentny i niezawodny układ, który pomaga sprawić, by systemy cyfrowe działały płynnie.Oszczędza energię, obsługuje różne napięcia i pozwala jej programować podczas już zainstalowanej, co ułatwia aktualizacje.Mimo że jest to teraz starszy układ, inni nadal go używają, ponieważ działa dobrze we wszystkich systemach.Jeśli potrzebujesz solidnego układu do kontrolowania logiki w swoim projekcie, ten jest świetną opcją.Skontaktuj się z nami już dziś, jeśli chcesz zamówić go luzem.

Arkusz danych pdf

EPM7256SQC208-10 Arkuszy danych:

Dysk oprogramowania 06/listopada/2020.pdf

Cylindryczne uchwyty akumulatorów. PDF

O nas

ALLELCO LIMITED

Czytaj więcej

Szybkie zapytanie.

Proszę wysłać zapytanie, natychmiast odpowiemy.

Często Zadawane Pytania [FAQ]

1. Jakie narzędzia do programowania są kompatybilne z EPM7256SQC208-10?

Możesz użyć oprogramowania Intel Quartus II (wcześniej Altera Quartus), wraz z programistą kompatybilnym z JTAG, takim jak USB-Blaster, do konfigurowania i zaprogramowania EPM7256SQC208-10 bezpośrednio w systemie.

2. Czy mogę wiele razy przeprogramować EPM7256SQC208-10?

Tak, EPM7256SQC208-10 obsługuje wiele cykli przeprogramowania przy użyciu programowalności opartej na systemie EEPROM, co czyni go idealnym do iteracyjnego rozwoju projektowania lub aktualizacji po wdrożeniu.

3. Czy EPM7256SQC208-10 może poradzić sobie z trudnymi warunkami pracy?

Działa niezawodnie w komercyjnym zakresie temperatur od 0 ° C do +70 ° C, co jest wystarczające do większości zastosowań przemysłowych i osadzonych, choć nie dla środowisk ekstremalnych lub motoryzacyjnych.

4. Czy nadal mogę zaprogramować EPM7256SQC208-10 bez usuwania go z płytki obwodu?

Tak.Chip obsługuje programowość w systemie (ISP) za pośrednictwem JTAG, umożliwiając przeprogramowanie go, gdy jest już przylutowany na tablicy, oszczędzając czas i wysiłek podczas rozwoju lub konserwacji.

5. Co sprawia, że EPM7256SQC208-10 jest lepszy niż standardowy mikrokontroler dla zadań logicznych?

W przeciwieństwie do mikrokontrolerów, EPM7256SQC208-10 to CPLD, który wyróżnia się w wykonywaniu równoległych operacji logicznych z precyzyjnym czasem.Jest to idealne, gdy potrzebujesz szybkiej, deterministycznej cyfrowej kontroli nad wieloma sygnałami.

Twierdzenia Demorgan wyjaśniono: Uproszczenie wyrażeń logicznych dla lepszego projektowania obwodu

na 2025/04/25

Podstawy i przykłady obwodu Norton Twierdzenie

na 2025/04/24

Popularne posty

-

Złożone komputery zestawu instrukcji: Jak zmieniły obliczenia?

na 8000/04/18 147766

-

Pinout i funkcje USB-C

na 2000/04/18 111994

-

Korzystanie z prymitywnych symulacji XILINX: kompleksowy przewodnik po projekcie i symulacji FPGA

na 1600/04/18 111351

-

Napięcia zasilania w elektronice: znaczenie VCC, VDD, VEE, VSS i GND

na 0400/04/18 83756

-

RJ45 Podręcznik złącza: pinout, okablowanie, typy kablowe i zastosowania

na 1970/01/1 79550

-

Ostateczny przewodnik po kodach kolorów drutu w nowoczesnych systemach elektrycznych

Sposób, w jaki nasze systemy elektryczne używają kolorów, nie jest tylko dla wyglądu.Każdy kolor drutu wskazuje teraz określoną funkcję, ułatwiając poprawną identyfikację komponentów elektrycznych ...na 1970/01/1 66951

-

Przewodnik zaworu oczyszczania: funkcja, objawy, testowanie i wymiana w celu optymalnej wydajności silnika

Zawór czyszczenia jest kluczową częścią systemu samochodu, który pomaga utrzymać w czystości powietrza poprzez zarządzanie oparami paliwowymi, zanim będą mogły uciec do atmosfery.To nie tylko pomag...na 1970/01/1 63094

-

Jakość (Q) Współczynnik: Równania i zastosowania

Współczynnik jakości lub „Q” jest ważny podczas sprawdzania, jak dobrze induktory i rezonatory działają w systemach elektronicznych, które wykorzystują częstotliwości radiowe (RF).„Q” mierzy, jak d...na 1970/01/1 63028

-

Osiągnięcie wydajności szczytowej przy maksymalnym twierdzeniu o przeniesieniu mocy

Twierdzenie o maksymalnym przeniesieniu mocy wyjaśnia, w jaki sposób energia ze źródła, takiego jak akumulator lub generator, płynie do podłączonego obciążenia.Pokazuje dokładny warunek, w którym o...na 1970/01/1 54094

-

A23 Specyfikacje i kompatybilność baterii

Akumulator A23 to mała akumulator w kształcie cylindra o wysokim napięciu.Nazywany również 23a, 23E lub Mn21, działa przy 12 woltach i znacznie wyższy niż akumulatory AA lub AAA.Jego specj...na 1970/01/1 52176