EPM7192SQC160-15 CPLD: Funkcje, pinout, programowanie i aplikacje

Ten przewodnik mówi o EPM7192SQC160-15, programowalnym układie logicznym z rodziny Max 7000s.Wyjaśnia, co chip może zrobić, jak działa i gdzie można go użyć.Pokazuje, w jaki sposób chip jest budowany w środku, co robi każdy szpilka i jak łączy się z innymi częściami.Przewodnik obejmuje również miejsce, w którym można użyć tego układu, jak zaprogramować go krok po kroku, jakie inne podobne układy istnieją i kto je tworzy.Katalog

Co to jest EPM7192SQC160-15?

. EPM7192SQC160-15 jest średniego zasięgu CPLD (złożone programowalne urządzenie logiczne) z rodziny Max 7000s, wykonana do niezawodnej cyfrowej kontroli logiki w systemach osadzonych i przemysłowych.Ten układ oferuje 192 makrokomórki i około 3750 bram logicznych, zapewniając wystarczającą pojemność do obsługi umiarkowanych zadań logicznych.Zawiera 124 piny we/wy i działa na zasilaniu 5V, z obsługą Multivolt I/O do interfejsu zarówno z systemami logicznymi 3,3 V, jak i 5 V.Jego programowalna architektura oparta na EEPROM w systemie oznacza, że możesz ją przeprogramować bezpośrednio w obwodzie za pomocą JTAG, bez konieczności dodatkowych komponentów lub pamięci zewnętrznej.Z oceną prędkości –15 obsługuje częstotliwości zegara systemu do około 76,9 MHz, oferując szybką i spójną wydajność czasu dla szeroko zakrojonych aplikacji cyfrowych.Rodzina Max 7000s znana jest z solidnej wydajności, pamięci EEPROM i elastycznego działania napięcia.

Szukasz EPM7192SQC160-15?Skontaktuj się z nami, aby sprawdzić aktualne zapasy, czas realizacji i ceny.

Modele CAD EPM7192SQC160-15

Symbol EPM7192SQC160-15

EPM7192SQC160-15 Stopprint

Model 3D EPM7192SQC160-15

Funkcje EPM7192SQC160-15

192 Macroceells: Urządzenie obejmuje 192 makrocelle, które służą jako podstawowe programowalne elementy.Te makrokomórki można skonfigurować do wdrażania szerokiej gamy kombinacyjnych i sekwencyjnych funkcji logicznych wymaganych w projektach cyfrowych.

Około 3750 bram logicznych: Oferuje równoważną pojemność logiczną około 3750 bram, dzięki czemu nadaje się do logiki kontroli średniej kompleksu, maszyn stanowych lub logiki kleju w systemach osadzonych.

Programowalność w systemie za pośrednictwem JTAG: Zawiera pamięć opartą na EEPROM, która umożliwia przeprogramowanie bezpośrednio w systemie za pomocą standardowego interfejsu JTAG, obsługując zarówno standardy IEEE 1149.1, jak i IEEE 1532.

Maksymalna częstotliwość do 125 MHz: Wewnętrzna logika może działać przy prędkościach zegara osiągających 125 MHz, umożliwiając szybkie przetwarzanie aplikacji wrażliwych na rozrząd.

Opóźnienie propagacji 7,5 ns: Chip oferuje niskie opóźnienie propagacji około 7,5 nanosekund, zapewniając szybką odpowiedź sygnału z wejścia na wyjście.

Obsługuje dostawę 5V z wielorakim we/wy: Urządzenie działa na zasilaniu podstawowym 5 V i obsługuje Multivolt I/O, co umożliwia kompatybilność z poziomami sygnału 5 V, jak i 3,3 V dla łatwej integracji z systemami mieszanego napięcia.

Programowalna prędkość notowa i wyjściowe wyjścia: Możesz kontrolować prędkości krawędzi sygnału dla redukcji EMI i wybrać wyjścia otwartego Draina dla przewodowej i logiki lub zmiany poziomu.

Sześć globalnych wyjściowych sygnałów włącza: Te globalne sygnały kontrolne umożliwiają włączenie lub wyłączenie wyników w wielu bankach we/wy w celu skutecznego zarządzania sygnałem.

Konfigurowalne klapki w makrocekom: Każdy makrokomórki zawiera flip-flop, który obsługuje ustawienie wstępnie, czystych, włączających zegar i indywidualną kontrolę, zapewniając zwiększoną elastyczność dla sekwencyjnego projektowania logiki.

Tryb niskiej mocy: Urządzenie zawiera funkcję oszczędzania energii, która może zmniejszyć zużycie energii makrocerowej o ponad 50%, co jest korzystne dla energooszczędnych zastosowań.

Wsparcie testowe JTAG-Scan-Scan : Urządzenia z 128 lub więcej makrokomórkami, podobnie jak ten, zawierają pełne funkcje testowania skanowania granicznego w celu wydajnej diagnostyki i walidacji na poziomie płyty.

Bit bezpieczeństwa w zakresie ochrony projektowania: Programowalny bit bezpieczeństwa zapewnia, że wewnętrzny projekt nie może być odczytany ani kopiowany, chroniąc własność intelektualną.

I/O kompatybilne z PCI: Struktura we/wy została zaprojektowana w celu spełnienia wymagań elektrycznych PCI, umożliwiając bezpośrednie interfejsy z systemami opartymi na PCI.

Zakres temperatur roboczych 0 ° C do 70 ° C: Standardowy zakres temperatury klasy komercyjnej sprawia, że urządzenie to odpowiednie dla większości zastosowań wewnętrznych i kontrolowanych.

Schemat pinout EPM7192SQC160-15

Ten schemat pokazuje układ pinu dla urządzeń EPM7192SQC160-15 i podobnych urządzeń Altera Max 7000s.Chip ma 160 pinów ułożonych wokół wszystkich czterech stron w kwadratowym pakiecie QFP.PIN 1 zaczyna się w lewym górnym rogu, a liczby idą w kierunku przeciwnym do ruchu wskazówek zegara.Każda strona ma 40 pinów.Mała kropka w górnym lewym śladach pin 1, która pomaga w prawidłowym rozmieszczeniu.Nazwa układu w centrum pokazuje, że jest zgodna z innymi modelami w tej samej rodzinie.Ten układ zapewnia wiele połączeń we/wy i jest przydatny do złożonych projektów logicznych.

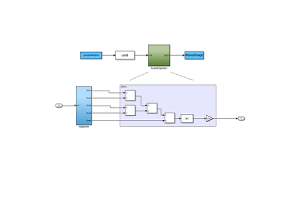

Schemat blokowy maksymalnego 7000s

Ten schemat blokowy pokazuje wewnętrzną strukturę MAX 7000S CPLD, w tym EPM7192SQC160-15.Chip jest podzielony na cztery główne sekcje zwane blokami tablic logicznych (laboratoryjne do d).Każde laboratorium ma 16 makrokomórków, które są małymi jednostkami logicznymi używanymi do budowania obwodów cyfrowych.Razem te laboratoria obsługują złożone operacje logiczne.

W centrum znajduje się programowalna tablica połączeń (PIA), która łączy wszystkie laboratoria i pozwala im udostępniać dane.Każde laboratorium wysyła i odbiera sygnały przez 36 kanałów, co daje elastyczne routing między blokami logiki.Wokół krawędzi znajdują się bloki kontrolne we/wy, które łączą 6 do 16 pinów we/wy do każdego laboratorium, umożliwiając urządzeniu połączenie z innymi częściami systemu.

Na górze pokazano globalne sygnały sterujące, takie jak zegary i wyjście.Sygnały te pomagają zarządzać tym, w jaki sposób dane poruszają się wewnątrz układu i gdy wyniki są aktywne.Ogólnie rzecz biorąc, schemat pokazuje, w jaki sposób EPM7192SQC160-15 organizuje swoją logikę i połączenia w celu obsługi niestandardowych projektów cyfrowych.

EPM7192SQC160-15 Specyfikacje

|

Typ |

Parametr |

|

Producent |

Altera |

|

Szereg |

Max® 7000s |

|

Opakowanie |

Taca |

|

Status części |

Przestarzały |

|

Typ programowalny |

W systemie programowalnym |

|

Czas opóźnienia TPD (1) Max |

15 ns |

|

Zasilanie napięcia - wewnętrzny |

4,75 V ~ 5,25 V. |

|

Liczba elementów/bloków logicznych |

12 |

|

Liczba makrokomórków |

192 |

|

Liczba bram |

3750 |

|

Liczba we/wy |

124 |

|

Temperatura robocza |

0 ° C ~ 70 ° C (TA) |

|

Typ montażu |

Mocowanie powierzchniowe |

|

Pakiet / obudowa |

160-BQFP |

|

Pakiet urządzeń dostawcy |

160-PQFP (28x28) |

|

Podstawowy numer produktu |

EPM7192 |

EPM7192SQC160-15 Zastosowania

Wbudowana logika kleju

EPM7192SQC160-15 jest idealny do wypełniania różnych urządzeń cyfrowych w systemach osadzonych.Można go używać do zarządzania komunikacją między mikrokontrolerów, układami pamięci i urządzeniami we/wy poprzez obsługę dekodowania adresu, kontroli magistrali i regulacji czasowych bez konieczności dyskretnej logiki.

Maszyny stanowe i logika kontroli

Dzięki 192 makrokomórkom układ jest odpowiedni do wdrażania niestandardowych maszyn stanu i logiki sterowania.Jest powszechnie stosowany w zadaniach automatyzacji, kontrolerach silników i systemach sterowania opartych na pomiarze, które wymagają niezawodnych i powtarzalnych przejść stanu.

Interfejsy protokołu komunikacji

Ten CPLD można zaprogramować w celu tworzenia lub translacji protokołów komunikacyjnych, takich jak UART, SPI, I²C lub niestandardowe formaty szeregowe.Umożliwia łatwą konfigurację i modyfikację bez zmiany sprzętu, dzięki czemu jest cenny dla interfejsu komunikacji.

Przetwarzanie wstępnego przetwarzania sygnału cyfrowego

Dzięki szybkiej prędkości logicznej i niskim opóźnieniu propagacji może obsługiwać proste zadania przetwarzania sygnału, takie jak filtrowanie, multipleksowanie lub wykrywanie krawędzi, zanim sygnały dotrą do głównego procesora lub układu DSP.

Tłumaczenie interfejsu i przesunięcie poziomu

Jego zdolność WE/O Multivolt obsługuje zarówno sygnały 3,3 V, jak i 5 V.To sprawia, że nadaje się do projektów zawierających komponenty działające na różnych poziomach napięcia, umożliwiając bezpieczne i wydajne tłumaczenie napięcia.

Szybkie aktualizacje prototypowania i systemu w systemie

Możesz użyć tego układu w systemach, które mogą wymagać częstych aktualizacji logiki.Struktura oparta na EEPROM i interfejs programowania JTAG umożliwiają przeprogramowanie logiki nawet po złożeniu płyty.

Test i diagnostyka na poziomie planszy

Dzięki obsłudze granicy za pośrednictwem JTAG testuje połączenia między układami na płytce drukowanej bez konieczności sond.Jest to przydatne podczas produkcji i diagnostyki w polu do wykrywania problemów z lutowaniem lub routingu.

EPM7192SQC160-15 Podobne części

• • EPM7192EQC160-20 (Altera)

To urządzenie pochodzi z tej samej serii Max 7000 i oferuje te same zasoby logiczne, 192 makrokomórki i 124 piny we/wy w 160-stykowym pakiecie PQFP.Działa w wolniejszym stopniu prędkości –20, co oznacza, że ma dłuższe opóźnienia propagacyjne (~ 20 ns), ale nadal zaspokaja potrzeby projektów bezkrytycznych.Jest to odpowiednia alternatywa dla zastosowań, w których gęstość logiczna jest ważna, ale ultra szybkie czas nie jest priorytetem, co czyni go idealnym dla projektów wrażliwych na koszty, które nadal wymagają równoważności funkcjonalnej.

• • EPM7192SQI160-10N (Altera)

Ta część jest również kompatybilna z logiką z EPM7192SQC160-15, oferując tę samą liczbę makrokomórków i I/OS.Wykorzystuje jednak –10 klasę prędkości, która obsługuje szybsze działanie z lepszym czasem (opóźnienie propagacji 10 ns).Obsługuje również rozszerzony zakres temperatur od –40 ° C do +85 ° C, co czyni go doskonałym substytutem zastosowań przemysłowych lub zewnętrznych.To sprawia, że jest to idealne, gdy wymagana jest większa prędkość i odporność na środowisko.

• • EPM7192SQC160-7 (Intel)

Jako wariant bezpośredniego przyspieszania EPM7192SQC160-15, wersja –7 zapewnia najszybszą wydajność w rodzinie, z opóźnieniami propagacji do 7,5 ns.Utrzymuje tę samą konfigurację PIN, specyfikację zasilania i gęstość logiczną, oferując wymianę upuszczania dla osób poszukujących lepszej prędkości bez zmiany zapotrzebowania na układ lub napięcie.To sprawia, że jest to najlepszy wybór dla projektów krytycznych czasowych wymagających szybszej reakcji sygnału podczas utrzymywania tego samego śladu projektu.

EPM7192SQC160-15 Kroki programowania

1. Wprowadź tryb ISP

Pierwszym krokiem jest przeniesienie urządzenia na tryb ISP (programowanie w systemie).Odbywa się to za pośrednictwem interfejsu JTAG.W trybie ISP wszystkie piny we/wy na urządzeniu są umieszczane w bezpiecznym trybie trójstanowym, aby zapobiec niezamierzonym zakłóceniu logicznym podczas programowania.Ta inicjalizacja zwykle zajmuje około 1 milisekundy.

2. Sprawdź identyfikator urządzenia

Unikalny identyfikator krzemowy jest osadzony w urządzeniu, aby sprawdzić, czy jest to poprawny model przed rozpoczęciem programowania.System przesuwa instrukcję odczytu i pobiera identyfikator za pomocą wiersza TDO (Data Test Out).Ta kontrola zapewnia, że narzędzie programowania jest podłączone do właściwego CPLD i unika błędów takich jak zastąpienie innej części.

3. Kasowanie masowe

Kasowanie masowe usuwa wszystkie wcześniej przechowywane dane w pamięci EEPROM CPLD.To przygotowuje układ do otrzymania nowej konfiguracji.Komenda usuwania inicjuje impuls, który zwykle trwa około 100 milisekund, zapewniając resetowanie wszystkich programowalnych komórek.

4. Program EEPROM

Nowe dane konfiguracyjne są ładowane do urządzenia przez przesuwanie adresu i bitów danych za pośrednictwem portu JTAG.Każda komórka pamięci jest zapisywana jeden po drugim, a impuls programowy zastosowano po każdym udanym cyklu zapisu.Proces ten określa strukturę logiczną, której użyje CPLD po zasilaniu.

5. Sprawdź EEPROM

Po programowaniu urządzenie wykonuje etap weryfikacji.Obejmuje to odczytanie każdej zaprogramowanej lokalizacji pamięci i porównywanie wartości wyjściowych z zamierzonymi danymi.Jeśli weryfikacja się nie powiedzie, proces musi zostać powtórzony.Ten krok gwarantuje, że konfiguracja została pomyślnie napisana.

6. Wyjdź z trybu ISP

Po zakończeniu weryfikacji wydano ostateczne polecenie wyjścia z trybu ISP.Urządzenie reaktywuje swoje piny we/wy i wznawia normalne działanie.Przejście to trwa również około 1 milisekundy i kończy cykl programowania w systemie.

EPM7192SQC160-15 Wymiary opakowania

• • Rozmiar ciała: 28 mm × 28 mm

• • Wysokość pakietu: 3,4 mm

• • Pin: 0,65 mm

EPM7192SQC160-15 Producent

EPM7192SQC160-15 został pierwotnie wyprodukowany przez Altera Corporation, firma znana z zaawansowanych programowalnych urządzeń logicznych.W 2015 r. Altera została przejęta przez Intel Corporation, a urządzenie jest teraz częścią grupy programowalnych rozwiązań Intel w ramach rodziny Max 7000s CPLD.Intel nadal obsługuje Legacy Altera Products, chociaż EPM7192SQC160-15 jest teraz klasyfikowany jako przestarzały w większości oficjalnych katalogów.Pomimo przerwanego statusu, historyczna reputacja Intela dotycząca niezawodności i dziedzictwo Altera w roztworach logicznych o wysokiej wydajności zapewniają dalsze popyt i dostępność za pośrednictwem drugorzędnych dystrybutorów.

Wniosek

EPM7192SQC160-15 jest użytecznym i elastycznym układem do obsługi cyfrowych zadań sterowania w wielu systemach elektronicznych.Oferuje wystarczającą moc logiczną do zadań, takich jak budowanie niestandardowych maszyn stanowych, sygnały obsługi i łączenie różnych urządzeń.Obsługuje różne poziomy napięcia, działa z szybkimi prędkościami i można go łatwo aktualizować za pośrednictwem JTAG.Jego wewnętrzna konstrukcja umożliwia płynny przepływ sygnału i łatwe zmiany logiki.Mimo że jest to teraz przerwane, nadal jest to świetna opcja dla starych lub bieżących projektów i można ją zastąpić podobnymi układami, które oferują szybsze lub szersze wsparcie temperatury.

Arkusz danych pdf

EPM7192SQC160-15 Arkuszy danych:

O nas

ALLELCO LIMITED

Czytaj więcej

Szybkie zapytanie.

Proszę wysłać zapytanie, natychmiast odpowiemy.

Często Zadawane Pytania [FAQ]

1. Czy mogę zaprogramować EPM7192SQC160-15 bez usunięcia go z płyty drukowanej?

Tak, Chip obsługuje programowanie w systemie (ISP) za pośrednictwem interfejsu JTAG, dzięki czemu można go zaprogramować lub przeprogramować bezpośrednio podczas lutowania na PCB, co upraszcza aktualizacje projektowe i zmniejsza przeróbkę.

2. Jakie oprogramowanie do programowania powinienem użyć dla EPM7192SQC160-15?

Możesz użyć oprogramowania Quartus II Altera (starsze wersje) do tworzenia projektów logicznych, kompilacji kodu i zarządzania procesem programowania opartym na JTAG.Quartus II obsługuje urządzenia MAX 7000S, takie jak EPM7192SQC160-15.

3. Czy EPM7192SQC160-15 wymaga pamięci zewnętrznej do obsługi?

Nie, ma wewnętrzną pamięć konfiguracyjną opartą na EEPROM.Cała konfiguracja logiczna jest przechowywana wewnątrz układu, więc do przechowywania stanów logicznych ani sekwencji rozruchowych nie jest potrzebna pamięć zewnętrzna.

4. Co sprawia, że EPM7192SQC160-15 nadaje się do użytku przemysłowego?

Jego solidna obsługa 5V, kompatybilność we/wy multivolt, szybkie przetwarzanie logiczne i pamięć nieulotna oparta na EEPROM sprawiają, że jest niezawodna dla systemów przemysłowych, które wymagają stabilnych i trwałych funkcji logicznych cyfrowych.

5. W jaki sposób EPM7192SQC160-15 obsługuje systemy mieszanego napięcia?

Dzięki obsłudze Multivolt we/wy urządzenie może interfejs zarówno z poziomami logiki 3,3 V, jak i 5 V, dzięki czemu jest idealny do systemów mieszanego sygnału i interfejsu z nowoczesnymi komponentami niskiego napięcia.

Dlaczego warto wybrać EPF10K100EFC484-3

na 2025/06/13

Co to jest przełącznik SPST i jak to działa?

na 2025/06/12

Popularne posty

-

Złożone komputery zestawu instrukcji: Jak zmieniły obliczenia?

na 8000/04/18 147778

-

Pinout i funkcje USB-C

na 2000/04/18 112033

-

Korzystanie z prymitywnych symulacji XILINX: kompleksowy przewodnik po projekcie i symulacji FPGA

na 1600/04/18 111352

-

Napięcia zasilania w elektronice: znaczenie VCC, VDD, VEE, VSS i GND

na 0400/04/18 83792

-

RJ45 Podręcznik złącza: pinout, okablowanie, typy kablowe i zastosowania

na 1970/01/1 79596

-

Ostateczny przewodnik po kodach kolorów drutu w nowoczesnych systemach elektrycznych

Sposób, w jaki nasze systemy elektryczne używają kolorów, nie jest tylko dla wyglądu.Każdy kolor drutu wskazuje teraz określoną funkcję, ułatwiając poprawną identyfikację komponentów elektrycznych ...na 1970/01/1 66976

-

Przewodnik zaworu oczyszczania: funkcja, objawy, testowanie i wymiana w celu optymalnej wydajności silnika

Zawór czyszczenia jest kluczową częścią systemu samochodu, który pomaga utrzymać w czystości powietrza poprzez zarządzanie oparami paliwowymi, zanim będą mogły uciec do atmosfery.To nie tylko pomag...na 1970/01/1 63110

-

Jakość (Q) Współczynnik: Równania i zastosowania

Współczynnik jakości lub „Q” jest ważny podczas sprawdzania, jak dobrze induktory i rezonatory działają w systemach elektronicznych, które wykorzystują częstotliwości radiowe (RF).„Q” mierzy, jak d...na 1970/01/1 63043

-

Osiągnięcie wydajności szczytowej przy maksymalnym twierdzeniu o przeniesieniu mocy

Twierdzenie o maksymalnym przeniesieniu mocy wyjaśnia, w jaki sposób energia ze źródła, takiego jak akumulator lub generator, płynie do podłączonego obciążenia.Pokazuje dokładny warunek, w którym o...na 1970/01/1 54097

-

A23 Specyfikacje i kompatybilność baterii

Akumulator A23 to mała akumulator w kształcie cylindra o wysokim napięciu.Nazywany również 23a, 23E lub Mn21, działa przy 12 woltach i znacznie wyższy niż akumulatory AA lub AAA.Jego specj...na 1970/01/1 52197