EPM7064STC100-7 CPLD: Funkcje, aplikacje i instrukcja programowania insystemu

EPM7064STC100-7 to potężny układ z serii Intel Max® 7000s, zaprojektowany do obsługi złożonych zadań w urządzeniach elektronicznych.W tym przewodniku omówiono główne funkcje i zastosowania EPM7064STC100-7, podkreślając jego zdolność do łatwego przeprogramowania, szybkiej pracy i elastycznej konstrukcji.Idealny do wielu różnych technologii, od małych gadżetów po duże maszyny przemysłowe - ten układ jest kluczowym elementem budowania zaawansowanych obwodów cyfrowych.Katalog

EPM7064STC100-7 Opis

. EPM7064STC100-7 jest złożonym programowalnym urządzeniem logicznym (CPLD) z serii Intel Max® 7000s.Ma 64 makrokomórki i 1250 bram, które pomagają w budowaniu złożonych obwodów cyfrowych.Ten układ działa z maksymalną prędkością 166,7 MHz, z opóźnieniem sygnału 7,5 nanosekund (NS).Ma 68 pinów wejściowych/wyjściowych (I/O), które działają z logiką 3,3 V i 5 V, co ułatwia używanie w różnych obwodach.Kluczową funkcją jest jego programowość w systemie 5.0 V (ISP) za pośrednictwem interfejsu JTAG (IEEE 1149.1).Oznacza to, że możesz go przeprogramować bez usuwania go z obwodu, ułatwiając testowanie i aktualizacje.Występuje w 100-pinowym cienkim quad płaskim opakowaniu (TQFP), który jest kompaktowym pakietem montowania powierzchni.Ten CPLD jest używany w systemach osadzonych, cyfrowym przetwarzaniu sygnałów, urządzeniach komunikacyjnych i automatyzacji przemysłowej.

Zapewniamy wysokiej jakości komponenty i dostosowane usługi, więc najlepiej złożyć z nami zamówienie masowe dla niezawodnych rozwiązań CPLD.

Funkcje EPM7064STC100-7

• • Logika o wysokiej gęstości: EPM7064STC100-7 został zaprojektowany z 64 makrokomórkami i 1250 użytecznymi bramkami, co czyni go wysoce odpowiednim do wdrażania złożonych funkcji logicznych w obwodach cyfrowych.Ta architektura o wysokiej gęstości umożliwia tworzenie skomplikowanych projektów logicznych przy jednoczesnym zachowaniu wydajności w programowalnych operacjach logicznych.Dobrze zoptymalizowana struktura makrokomórka zapewnia skuteczne wykorzystanie dostępnych zasobów, obsługując zaawansowane implementacje logiczne kombinacyjne i sekwencyjne.

• • Szybka wydajność: Zbudowany do szybkiego przetwarzania, EPM7064STC100-7 działa z maksymalną częstotliwością wewnętrzną 166,7 MHz, umożliwiając szybkie wykonywanie funkcji logicznych.Opóźnienie propagacji 7,5 ns zapewnia minimalne opóźnienie.Ta zdolność szybkiego przełączania zwiększa zdolność urządzenia do efektywnego obsługi szybkiego przetwarzania danych, kondycjonowania sygnałów i kontroli, co czyni go niezawodnym wyborem wymagających systemów cyfrowych.

• • Wszechstronny I/O: Z 68 programowalnymi pinami wejściowymi/wyjściowymi EPM7064STC100-7 oferuje wyjątkową elastyczność integracji z różnymi projektami obwodów.Obsługując zarówno poziomy logiki 3,3 V, jak i 5 V, umożliwia bezproblemową kompatybilność z różnymi napięciami systemowymi, eliminując potrzebę dodatkowych przesuwników poziomu napięcia.Ta zdolność adaptacyjna sprawia, że jest odpowiedni do zastosowań w środowiskach mieszanego napięcia, zapewniając szerokie zastosowanie w systemach wbudowanych, kontrolach przemysłowych i sieciach komunikacyjnych.

• • Programowalność w systemie (ISP): Jedną z zalet EPM7064STC100-7 jest jego programowość w systemie 5,0 V (ISP), ułatwiona przez IEEE STD.1149.1 interfejs JTAG.Ta funkcja umożliwia przeprogramowanie i modyfikowanie funkcji logicznych bez polegania lub fizycznego usuwania urządzenia, uproszczenia konserwacji, debugowania i iteracyjnego rozwoju.Możliwość ISP zmniejsza przestoje i zwiększa elastyczność aktualizacji oprogramowania układowego, dzięki czemu jest nieoceniona dla dynamicznych i rekonfigurowalnych projektów cyfrowych.

Modele CAD EPM7064STC100-7

EPM7064STC100-7 Symbol

EPM7064STC100-7 Footprint

Model 3D EPM7064STC100-7

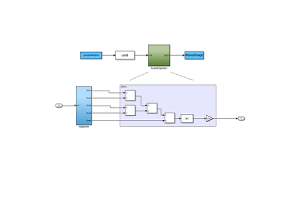

Schemat blokowy EPM7064STC100-7

. Schemat blokowy EPM7064STC100-7 pokazuje, w jaki sposób elementy logiczne układu są podłączone i kontrolowane.Ma cztery bloki macierzy logicznej (laboratorium), oznaczone A, B, C i D, każdy zawierający 16 makrokomórków.Te makrokomórki wykonują funkcje logiczne i łączą się za pośrednictwem programowalnej tablicy połączeń (PIA), która umożliwia elastyczne routing sygnałów.Każde laboratorium jest połączone z blokiem sterującym we/wy, obsługując do 16 pinów wejściowych/wyjściowych na laboratorium.Schemat pokazuje również globalne sygnały kontrolne (GCLK1, GCLK2, OE1 i GCLRN), które pomagają w zarządzaniu funkcjami zegarowymi i resetowaniem dla układu.Niektóre bramy logiczne przetwarzają te sygnały, zanim osiągną różne części systemu.Projekt EPM7064STC100-7 pozwala na stosowanie go w różnych programowalnych aplikacjach logicznych, takich jak maszyny stanowe, dekodowanie adresów i inne niestandardowe obwody cyfrowe.Jego elastyczne połączenia łączące zapewniają wydajny przepływ sygnału i niezawodne działanie.

EPM7064STC100-7 Specyfikacje

|

Typ |

Parametr |

|

Producent |

Altera/Intel |

|

Szereg |

Max® 7000s |

|

Opakowanie |

Taca |

|

Status części |

Przestarzały |

|

Typ programowalny |

W systemie programowalnym |

|

Czas opóźnienia TPD (1) Max |

7,5 ns |

|

Zasilanie napięcia - wewnętrzny |

4,75 V ~ 5,25 V. |

|

Liczba elementów/bloków logicznych |

4 |

|

Liczba makrokomórków |

64 |

|

Liczba bram |

1250 |

|

Liczba we/wy |

68 |

|

Temperatura robocza |

0 ° C ~ 70 ° C (TA) |

|

Typ montażu |

Mocowanie powierzchniowe |

|

Pakiet / obudowa |

100-TQFP |

|

Pakiet urządzeń dostawcy |

100-TQFP (14x14) |

|

Podstawowy numer produktu |

EPM7064 |

EPM7064STC100-7 Insystem Programming (ISP)

EPM7064STC100-7, część rodziny MAX 7000S CPLD, jest zgodna z sześciostopniową sekwencją programowania systemu (ISP), aby zapewnić prawidłową konfigurację.Ten proces umożliwia zaprogramowanie urządzenia bez usuwania go z płyty drukowanej.Proces ISP obejmuje przesunięcie instrukcji, adresów i danych za pośrednictwem PIN TDI (dane testowe w) podczas pobierania odpowiedzi za pomocą PIN TDO (danych testowych).

Pierwszy etap, Wprowadź dostawcę usług internetowych, zapewnia płynne przejście pinów we/wy z trybu użytkownika do trybu ISP i wymagają około 1 ms.Następnie następuje Sprawdź id, gdzie odczytany jest silikonowy identyfikator urządzenia, aby potwierdzić prawidłowy cel.Następnie Wysyłanie luzem Przesunięcia etapowe w instrukcjach usuwania i stosuje impuls kasowania 100mm, usuwając wszystkie istniejące dane w komórkach EEPROM.. Program Następuje etap, w którym adresy i dane są sekwencyjnie przenoszone na urządzenie, stosując impulsy programowe do konfigurowania komórek EEPROM.Każdy adres musi być zaprogramowany indywidualnie, dzięki czemu ten krok był czasochłonny w zależności od liczby komórek EEPROM w urządzeniu.

Po zakończeniu programowania, Zweryfikować Etap zapewnia poprawnie przechowywanie danych.Tutaj impulsy odczytu są stosowane do komórek EEPROM, a pobrane dane są porównywane z oczekiwanymi wartościami.W przypadku znalezienia rozbieżności konieczne może być przeprogramowanie.Wreszcie Wyjdź z ISP Etap zapewnia, że piny we/wy przechodzą z powrotem do trybu użytkownika, wymagające kolejnych 1 ms.Na całkowity czas programowania lub weryfikacji wpływają dwa główne czynniki: czas impulsu, wymagany do usuwania EEPROM, programowania i operacji odczytu oraz czas zmiany czasu, który zależy od częstotliwości TCK (zegar testu) i liczby cykli potrzebnych do przesyłania instrukcji, adresów i danych.Ponieważ różne urządzenia zdolne do ISP mają różną liczbę komórek EEPROM, zarówno czas ustalany, jak i zmienne są unikalne dla każdego urządzenia.Całkowity czas ISP można obliczyć jako funkcję częstotliwości TCK, liczby urządzeń docelowych i architektury EEPROM.

EPM7064STC100-7 Zastosowania

Systemy wbudowane

EPM7064STC100-7 jest szeroko stosowany w wbudowanych aplikacjach systemowych, gdzie służy jako elastyczne programowalne rozwiązanie logiczne do kontrolowania różnych peryferyjnych, sygnałów przetwarzania i wdrażania niestandardowych protokołów.Jego zdolność do interfejsu z mikrokontrolerami i czujnikami pozwala zoptymalizować wydajność systemu przy jednoczesnym zachowaniu kompaktowego śladu.Dzięki szybkiej obsługi i niskim zużyciu energii jest doskonałym wyborem dla wbudowanych zastosowań wymagających niezawodności i wydajności.

Cyfrowe przetwarzanie sygnału (DSP)

W cyfrowym przetwarzaniu sygnałów EPM7064STC100-7 odgrywa rolę we wdrażaniu filtrów, modulacji sygnału i różnych funkcjach matematycznych.Jego szybkie prędkości przełączania i niskie opóźnienie propagacji sprawiają, że nadaje się do obsługi zadań przetwarzania danych o wysokiej częstotliwości, zapewniając minimalne opóźnienie w konwersji i manipulacji sygnału.Jest powszechnie stosowany w przetwarzaniu audio, telekomunikacji i systemach radarowych.

Komunikacja danych

EPM7064STC100-7 jest szeroko wykorzystywany w systemach sieciowych i komunikacji danych ze względu na jego zdolność do obsługi operacji intensywnych do logiki, takich jak routing danych, buforowanie i korekcja błędów.Jego programowalne możliwości we/wy pozwalają dostosować się do różnych protokołów komunikacyjnych, co czyni go cennym komponentem w przełącznikach Ethernet, routerach i infrastrukturze telekomunikacyjnej.Jego obsługa programowalności w systemie (ISP) umożliwia również aktualizacje w terenie, poprawę możliwości adaptacji w dynamicznych środowiskach sieciowych.

Automatyzacja przemysłowa

Zastosowania przemysłowe wymagają wysokiej niezawodności, trwałości i niskiego zużycia energii, dzięki czemu EPM7064STC100-7 jest preferowanym wyborem dla programowalnych kontrolerów logicznych (PLC), systemów sterowania silnikami i automatycznym sprzętem testowym.Dzięki programowalności w systemie opartym na JTAG zapewnia on możliwość udoskonalania procesów automatyzacji bez wymagania fizycznego usunięcia lub przeprojektowania.Jego wszechstronność zgodności napięcia sprawia, że nadaje się również do interfejsu z szeroką gamą czujników i siłowników używanych w warunkach przemysłowych.

EPM7064STC100-7 Podobne części

• • EPM7064STC44-10N

• • EPM7064STC100-6

• • EPM7064STC100-10

EPM7064STC100-7 Zalety

Programowalność w systemie (ISP)

Jedną z największych zalet EPM7064STC100-7 jest jego zdolność do przeprogramowania w systemie.To eliminuje potrzebę usunięcia układu w celu aktualizacji, skracania czasu konserwacji i poprawy wydajności.Możesz wdrożyć modyfikacje projektowe bez przerywania produkcji, co czyni ją opłacalnym rozwiązaniem dla długoterminowych projektów.

Szybka wydajność

Urządzenie obsługuje wysoką wewnętrzną częstotliwość roboczą do 166,7 MHz, umożliwiając szybkie przetwarzanie danych i czasy reakcji.To sprawia, że idealnie nadaje się do aplikacji wymagających przetwarzania sygnału, kontroli logiki i szybkich interfejsu, zapewniając gładsze i bardziej niezawodne działanie systemu.

Wszechstronne wsparcie we/wy

Przy do 68 konfigurowalnych pinów we/wy i kompatybilności z wieloma poziomami napięcia (3,3 V, 5 V i opcjami tolerancyjnymi dla 2,5 V, 3,3 V i 5 V), EPM7064STC100-7 oferuje elastyczność w projektowaniu systemu.Umożliwia bezproblemową integrację z różnymi obwodami i obsługuje środowiska mieszanego napięcia, zmniejszając problemy z kompatybilnością z innymi komponentami.

Niezawodne działanie w różnych środowiskach

Zaprojektowany do funkcjonowania w zakresie temperatur od 0 ° C do 70 ° C, EPM7064STC100-7 zapewnia spójne i stabilne działanie w różnych warunkach.Ta niezawodność sprawia, że jest to preferowany wybór aplikacji, w których wymagana jest stabilność środowiska, takie jak automatyzacja przemysłowa, telekomunikacja i wbudowane systemy sterowania.

EPM7064STC100-7 Pakiet Pin-Out-Out

EPM7064STC100-7 to CPLD (złożone programowalne urządzenie logiczne) z serii Max 7000S Altera, umieszczonego w 100-pinowym cienkim quad płaskim (TQFP-100).Ten typ pakietu jest zaprojektowany do zastosowań do montażu powierzchniowego, oferując równowagę o wysokiej gęstości pinów i kompaktowej wielkości.. Pin-Out Schemat Kontynuuje schemat numeracji przeciwnych do ruchu wskazówek zegara, z pinem 1 umieszczonym w lewym górnym rogu opakowania.Poruszając się w kierunku przeciwnym do ruchu wskazówek zegara, pierwsze 25 pinów zajmuje lewą stronę, piny 26 do 50 jest ustawione wzdłuż dolnej krawędzi, piny 51 do 75 kontynuują po prawej stronie, a piny 76 do 100 są rozmieszczone wzdłuż górnej krawędzi.. Pakiet TQFP-100 Cechy cienkie prowadzące rozciągające się na zewnątrz ze wszystkich czterech stron płaskiego, kwadratowego ciała.Ta konstrukcja zwiększa kompatybilność montowania powierzchni przy jednoczesnym zachowaniu odpowiedniego odstępu nad stypem w celu łatwego lutowania i montażu.Dokonanie ołowiu (odległość między sąsiednimi pinami) jest zazwyczaj 0,5 mm, optymalizując integralność sygnału przy jednoczesnym minimalizowaniu ogólnego śladu.

EPM7064STC100-7 Producent

EPM7064STC100-7 to CPLD (złożone programowalne urządzenie logiczne), opracowane przez Altera, spółkę półprzewodników znaną z programowalnych rozwiązań logicznych.W 2015 roku Intel nabył Altera, integrując linie produktów FPGA i CPLD z grupą programowalnych rozwiązań Intel (PSG).Od tego czasu EPM7064STC100-7 był oznakowany pod Intelem, chociaż został oznaczony jako przestarzały.Intel, jako producent, utrzymywał starsze obsługę CPLD serii Max® 7000s, w tym ten model, jednocześnie stopniowo przesuwając swój koncentracja na nowoczesnych technologiach FPGA i programowalnych technologii logicznych.

Wniosek

EPM7064STC100-7 łączy złożone funkcje, szybką wydajność i łatwe aktualizacje w jednym układie, co dowodzi jej wartości w trudnych konfiguracjach cyfrowych.Ten przewodnik pokazał, jak to działa, do czego jest używany i jak pasuje do różnych systemów elektronicznych.Pomaga sprawić, by urządzenia działały płynnie i wydajnie, udowadniając, że nadal jest bardzo przydatne w wielu aplikacjach.Ten przewodnik zawiera wyraźny widok, w jaki sposób EPM7064STC100-7 może pomóc w skutecznym ulepszeniu projektów elektronicznych i operacji systemowych.

Arkusz danych pdf

EPM7064STC100-7 Arkusze danych:

O nas

ALLELCO LIMITED

Czytaj więcej

Szybkie zapytanie.

Proszę wysłać zapytanie, natychmiast odpowiemy.

Często Zadawane Pytania [FAQ]

1. W jaki sposób opóźnienie propagacji 7,5NS wydajności obwodu uderzenia EPM7064STC100-7?

Opóźnienie propagacji 7,5N zapewnia przetwarzanie sygnałów o niskiej opóźnieniu, dzięki czemu CPLD nadaje się do aplikacji szybkich, takich jak cyfrowe przetwarzanie sygnałów (DSP), systemy komunikacyjne i automatyzacja przemysłowa, które wymagają precyzyjnej kontroli czasu.

2. Czy EPM7064STC100-7 można zaprogramować za pomocą nowoczesnych narzędzi programistycznych?

Tak, można go zaprogramować przy użyciu oprogramowania Intel Quartus II (wcześniej Altera Quartus) wraz z odpowiedniego programisty JTAG.Jednak obsługa starszych CPLD, takich jak EPM7064STC100-7, może być ograniczone w nowszych wersjach Quartus, więc może być konieczne użycie starszych wersji, takich jak Quartus II 13.0 SP1, które nadal obsługują urządzenia Max® 7000s.

3. Czy EPM7064STC100-7 obsługuje środowiska mieszanego napięcia?

Tak, obsługuje zarówno poziomy logiki 3,3 V, jak i 5 V, co czyni go kompatybilnym z szeroką gamą obwodów cyfrowych.Ta elastyczność jest przydatna do interfejsu starszych komponentów 5 V z nowoczesnymi systemami 3,3 V bez dodatkowych obwodów zmieniających poziom.

4. Jaka jest najlepsza metoda rozwiązywania problemów z EPM7064STC100-7?

Aby rozwiązywać problemy, możesz użyć Analizatora logicznego Quartus SignalTap II lub zewnętrznych oscyloskopów i analizatorów logicznych do monitorowania sygnałów.Jeśli debugowanie problemów z programowaniem JTAG upewnij się, że połączenia TDI, TDO, TCK i TMS są prawidłowe i że używasz kompatybilnego blastera USB lub programisty BytbasterMV.

5. Czy mogę zaprogramować EPM7064STC100-7 bez usuwania go z mojej płyty drukowanej?

Tak.Programowość systemu 5.0 V (ISP) za pośrednictwem JTAG (IEEE 1149.1) pozwala przeprogramować urządzenie, gdy pozostaje ono w systemie.To sprawia, że aktualizacje oprogramowania układowego, debugowanie i testowanie jest znacznie bardziej wydajne w porównaniu z tradycyjnymi CPLD.

Kompletny przewodnik po rezystorze 10K: Kod koloru, aplikacje i obwód

na 2025/03/10

Kondensatory vs. baterie: co jest najlepsze dla twoich potrzeb energetycznych?

na 2025/03/7

Popularne posty

-

Złożone komputery zestawu instrukcji: Jak zmieniły obliczenia?

na 8000/04/18 147778

-

Pinout i funkcje USB-C

na 2000/04/18 112033

-

Korzystanie z prymitywnych symulacji XILINX: kompleksowy przewodnik po projekcie i symulacji FPGA

na 1600/04/18 111352

-

Napięcia zasilania w elektronice: znaczenie VCC, VDD, VEE, VSS i GND

na 0400/04/18 83790

-

RJ45 Podręcznik złącza: pinout, okablowanie, typy kablowe i zastosowania

na 1970/01/1 79596

-

Ostateczny przewodnik po kodach kolorów drutu w nowoczesnych systemach elektrycznych

Sposób, w jaki nasze systemy elektryczne używają kolorów, nie jest tylko dla wyglądu.Każdy kolor drutu wskazuje teraz określoną funkcję, ułatwiając poprawną identyfikację komponentów elektrycznych ...na 1970/01/1 66976

-

Przewodnik zaworu oczyszczania: funkcja, objawy, testowanie i wymiana w celu optymalnej wydajności silnika

Zawór czyszczenia jest kluczową częścią systemu samochodu, który pomaga utrzymać w czystości powietrza poprzez zarządzanie oparami paliwowymi, zanim będą mogły uciec do atmosfery.To nie tylko pomag...na 1970/01/1 63110

-

Jakość (Q) Współczynnik: Równania i zastosowania

Współczynnik jakości lub „Q” jest ważny podczas sprawdzania, jak dobrze induktory i rezonatory działają w systemach elektronicznych, które wykorzystują częstotliwości radiowe (RF).„Q” mierzy, jak d...na 1970/01/1 63043

-

Osiągnięcie wydajności szczytowej przy maksymalnym twierdzeniu o przeniesieniu mocy

Twierdzenie o maksymalnym przeniesieniu mocy wyjaśnia, w jaki sposób energia ze źródła, takiego jak akumulator lub generator, płynie do podłączonego obciążenia.Pokazuje dokładny warunek, w którym o...na 1970/01/1 54097

-

A23 Specyfikacje i kompatybilność baterii

Akumulator A23 to mała akumulator w kształcie cylindra o wysokim napięciu.Nazywany również 23a, 23E lub Mn21, działa przy 12 woltach i znacznie wyższy niż akumulatory AA lub AAA.Jego specj...na 1970/01/1 52197