EP2S60F672C4 FPGA: Funkcje, aplikacje, programowanie i podręcznik arkusza danych

W tym przewodniku otrzymasz wyraźny przegląd EP2S60F672C4, potężnego FPGA z rodziny Stratix II Intela.Dowiesz się o jego głównych funkcjach, architekturze, strukturze bloków i specyfikacjach technicznych, aby zrozumieć, w jaki sposób pasuje do zaawansowanych projektów cyfrowych.Przegląda także kroki programowania, aplikacje, zalety i wady, dzięki czemu można dokładnie zobaczyć, gdzie i jak można użyć tego urządzenia.Katalog

Co to jest EP2S60F672C4?

. EP2S60F672C4 jest FPGA o wysokiej gęstości z Intela (wcześniej Altera), należącego do rodziny Stratix II.Zbudowany na miedzianym procesie SRAM o mocy 90 nm, 1,2 V, zapewnia znaczną pojemność logiczną w pakiecie 672-balowym FBGA, co czyni go idealnym dla złożonych systemów cyfrowych.W ramach serii EP2S urządzenie „60” znajduje się w zakresie od połowy do urzędu składu Stratix II, oferując silną równowagę gęstości logicznej, pamięci osadzonej i zasobów we/wy.Znana z solidnej architektury i niezawodności, ta FPGA pozostaje zaufanym wyborem w wielu zaawansowanych projektach.

Szukasz EP2S60F672C4?Skontaktuj się z nami, aby sprawdzić aktualne zapasy, czas realizacji i ceny.

Modele CAD EP2S60F672C4

Symbol EP2S60F672C4

Ślad EP2S60F672C4

Model 3D EP2S60F672C4

Funkcje EP2S60F672C4

• • Zaawansowany proces 90 nm, 1,2 V CMOS

EP2S60F672C4 jest wytwarzany w procesie CMO CMO miedzianym 90 nm, który działa przy napięciu rdzeniowym 1,2 V.Ta technologia umożliwia dużą prędkość, zmniejszone zużycie energii i większą gęstość logiczną w porównaniu ze starszymi pokoleniami FPGA.

• • Adaptacyjna architektura modułu logicznego (ALM)

Urządzenie wykorzystuje AMM jako logiczny element konstrukcyjny zamiast tradycyjnych elementów logicznych.Architektura ta poprawia wykorzystanie zasobów, umożliwiając efektywne wdrażanie bardziej złożonych funkcji logicznych w tym samym obszarze krzemu.

• • Wysoka gęstość logiczna

Z około 60 440 elementami logicznymi (24 176 jałmużny) FPGA obsługuje duże i wyrafinowane projekty cyfrowe.Ta wysoka pojemność sprawia, że nadaje się do zastosowań, takich jak przetwarzanie sygnałów, komunikacja i wbudowane systemy sterowania.

• • Pamięć Trimatrix ™ na chipie

EP2S60F672C4 integruje trzy typy bloków pamięci RAM (M512, M4K i M-RAM), aby zapewnić w sumie około 2,4 mbit pamięci osadzonej.Ta mieszanka pozwala skutecznie wdrażać małe FIFO, średnie bufory i duże wspomnienia z podwójnym portem.

• • Dedykowane bloki DSP

Urządzenie zawiera 36 dedykowanych bloków DSP zaprojektowanych do operacji arytmetycznych, takich jak mnożenie, akumulacje i filtrowanie FIR.Te bloki zwiększają wydajność w zadaniach związanych z obliczeniami, jednocześnie zapisując ogólne zasoby logiczne.

• • Szybkie we/wy i integralność sygnału

Obsługuje różne jednokierunkowe i różnicowe standardy we/wy wraz z obwodem dynamicznego wyrównania fazy (DPA).Funkcje te umożliwiają stabilne, szybkie przesyłanie danych do 1 Gb / s, zapewniając niezawodną komunikację z komponentami zewnętrznymi.

• • Bogaty obsługa interfejsu pamięci zewnętrznej

FPGA jest kompatybilna z DDR, DDR2, QDR II, RLDRAM II i innymi standardami pamięci.Wbudowane obsługa interfejsu upraszcza projektowanie płyty i osiąga wysoką przepustowość danych dla aplikacji intensywnie wymagających pamięci.

• • Elastyczne zarządzanie zegarami

Do 12 PLL na chipie umożliwia mnożenie zegara, podział, przesuwanie fazy i przełączanie bez usterki.Możesz dostroić domeny zegarowe i zmniejszyć drganie, obsługując wewnętrzne częstotliwości zegara do 500–550 MHz.

• • Szyfrowanie i rekonfiguracja BitStream

EP2S60F672C4 obsługuje szyfrowanie BitStream oparte na AES w celu zabezpieczenia własności intelektualnej.Oferuje również możliwość zdalnej rekonfiguracji, umożliwiając aktualizacje w polu bez wymiany urządzenia.

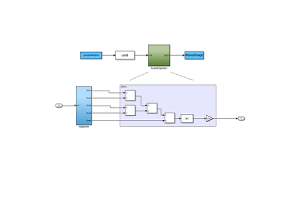

Schemat blokowy Stratix II

Schemat blokowy Stratix II, jak pokazano dla EP2S60F672C4, ilustruje wewnętrzny układ zasobów logicznych, pamięci i DSP, które tworzą rdzeń FPGA.Bloki macierzy logicznej (laboratoria) są ułożone w zwykłej siatce, otoczonej wbudowanymi kolumnami RAM i DSP, które zapewniają szybkie możliwości arytmetyczne i przechowywania na chipie.Peryferyjne elementy we/wy i sieci zegara opracowują tę strukturę, umożliwiając wydajną kontrolę przesyłania danych i pomiaru czasu między urządzeniami FPGA i zewnętrznymi.Ten schemat jest ważny, ponieważ pomaga zrozumieć, w jaki sposób różne bloki funkcjonalne są fizycznie zorganizowane, umożliwiając im optymalizację umieszczania, routingu i ogólnej wydajności systemu.

Schemat Banków I/O Stratix II

Ten schemat banków we/wy Stratix II ilustruje, w jaki sposób kołki wejściowe/wyjściowe EP2S60F672C4 są pogrupowane i jakie standardy elektryczne obsługuje każda grupa.Każdy bank we/wy został zaprojektowany do obsługi określonych poziomów napięcia, typów sygnalizacji i funkcji, takich jak standardy wejściowe LVTTL, SSTL, LVDS lub Zegar.Układ pokazuje, w jaki sposób różne banki (np. 1, 2, 5, 6 vs. 3, 4, 7, 8 itd.) Są zoptymalizowane pod kątem ogólnego poziomu interpretacji lub szybkiej sygnalizacji różnicowej, w tym obsługę wejść zegarowych LVDS/LVPECL na krawędziach.Zrozumienie tej struktury jest ważne przy przypisywaniu pinów, ponieważ właściwy wybór banku zapewnia kompatybilność elektryczną, upraszcza routing planszy i maksymalizuje wydajność FPGA w dużych konstrukcjach.

Specyfikacje EP2S60F672C4

|

Typ |

Parametr |

|

Producent |

Altera/Intel |

|

Szereg |

Stratix® II |

|

Opakowanie |

Taca |

|

Status części |

Przestarzały |

|

Liczba laboratoriów/CLB |

3022 |

|

Liczba elementów/komórek logicznych |

60,440 |

|

Całkowite bity RAM |

2 544,192 |

|

Liczba we/wy |

492 |

|

Napięcie - zasilanie |

1,15 V ~ 1,25 V |

|

Typ montażu |

Mocowanie powierzchniowe |

|

Temperatura robocza |

0 ° C ~ 85 ° C (TJ) |

|

Pakiet / obudowa |

672-BBGA |

|

Pakiet urządzeń dostawcy |

672-FBGA (27 × 27) |

|

Podstawowy numer produktu |

EP2S60 |

Aplikacje EP2S60F672C4

1. Cyfrowe przetwarzanie sygnału (DSP) i filtrowanie

EP2S60F672C4 dobrze nadaje się do wdrażania wysokowydajnych funkcji DSP, takich jak filtry FIR i IIR, przetwarzanie FFT i złożone operacje arytmetyczne.Jego dedykowane bloki DSP skutecznie obsługują mnożenie i gromadzenie się, uwalniając ogólne zasoby logiczne do innych zadań.Pamięć Trimatrix ™ na chipu umożliwia płynne buforowanie danych i rurociąg, co jest idealne do przetwarzania w czasie rzeczywistym przy wysokiej szybkości próbkowania.To sprawia, że urządzenie jest idealne do zaawansowanych aplikacji sygnałowych audio, wideo i radarowych.

2. Szybka komunikacja i tworzenie sieci

Szybkie interfejsy we/wy FPGA i dynamiczne wyrównanie fazy (DPA) obsługują niezawodne, transmisja danych na poziomie Gigabit.Może wdrażać protokoły komunikacyjne i funkcje warstw fizycznych dla systemów takich jak routery, przełączniki i połączenia płynów płynnych.Dzięki dużej pojemności logicznej i elastycznymi PLL, może zarządzać złożonym czasem i konwersjami protokołu między wieloma szybkimi interfejsami.Możliwości te sprawiają, że jest to silne dla infrastruktury telekomunikacyjnej i sprzętu sieciowego o dużej przepustowości.

3. Kontrolery pamięci i systemy przetwarzania danych

EP2S60F672C4 obsługuje różne interfejsy pamięci zewnętrznej, w tym DDR, DDR2, RLDRAM II i QDR II, co czyni go idealnym do projektowania kontrolerów pamięci o wysokiej pasma.Może obsługiwać buforowanie danych, generowanie adresów i arbitraż przy dużych prędkościach przy minimalnym opóźnieniu.Połączenie szybkich sieci i wbudowanych bloków pamięci RAM umożliwia wydajne zarządzanie dużymi strumieniami danych.To sprawia, że FPGA nadaje się do przetwarzania obrazu, strumieniowania wideo i platform obliczeniowych naukowych, które opierają się na ciężkiej przepustowości danych.

4. Niestandardowa logika i przyspieszenie osadzone

Dzięki ponad 60 000 elementów logicznych i bogatym zarządzaniu zegarkiem FPGA może hostować niestandardowe akceleratory sprzętowe dla określonych algorytmów.Projektanci często używają go do odciążenia zadań intensywnie obliczeniowo z procesorów, takich jak szyfrowanie, parsowanie protokołu lub pętle sterowania w czasie rzeczywistym.Może również zintegrować wiele funkcjonalnych bloków, dzięki czemu nadaje się do złożonych projektów podobnych do SOC.Ta elastyczność sprawia, że jest cenna w aplikacjach takich jak automatyzacja przemysłowa, systemy bezpieczeństwa i jednostki kontroli lotniczej.

5. Prototypowe i edukacyjne platformy rozwoju

Urządzenie EP2S60 jest powszechnie spotykane w zestawach rozwojowych FPGA stosowanych do prototypowania, testowania i badań akademickich.Jego równowaga pojemności logicznej, liczby we/wy i możliwości DSP pozwala inżynierom i studentom wdrażać i weryfikować pełne systemy na jednym chipie.Obsługuje szybką iterację projektów cyfrowych, umożliwiając weryfikację sprzętu przed zaangażowaniem się w rozwój ASIC.Wiele uniwersytetów i laboratoriów badawczo -rozwojowych używa go do nauczania zaawansowanych koncepcji projektowania cyfrowego i przetwarzania sygnałów.

EP2S60F672C4 Podobne części

|

Specyfikacja |

EP2S60F672C4 |

EP2S60F672C3N |

EP2S60F672C5 |

EP2S60F672C5N |

EP2S60F672I4

|

EP2S60F672I3N |

|

Rodzina / seria |

Stratix II |

Stratix II |

Stratix II |

Stratix II |

Stratix II |

Stratix II |

|

Elementy logiczne (LE) |

60,440 |

60,440 |

60,440 |

60,440 |

60,440 |

60,440 |

|

Jałmużna |

24 176 |

24 176 |

24 176 |

24 176 |

24 176 |

24 176 |

|

Pakiet |

FBGA-672 |

FBGA-672 |

FBGA-672 |

FBGA-672 |

FBGA-672 |

FBGA-672 |

|

Stopień prędkości |

C4 (STD) |

C3 (szybciej) |

C5 (szybciej) |

C5 (szybciej) |

I4 (std) |

I3 (szybciej) |

|

Ocena temperatury |

Komercyjny (0 ~ 70 ° C) |

Handlowy |

Handlowy |

Handlowy |

Przemysłowy (-40 ~ 100 ° C) |

Przemysłowy (-40 ~ 100 ° C) |

|

Piny we/wy |

492 |

492 |

492 |

492 |

492 |

492 |

|

Pamięć na chipie |

2,4 mbit |

2,4 mbit |

2,4 mbit |

2,4 mbit |

2,4 mbit |

2,4 mbit |

|

Napięcie rdzenia |

1.2 v |

1.2 v |

1.2 v |

1.2 v |

1.2 v |

1.2 v |

|

Kluczowa różnica |

Wyjściowa prędkość komercyjna |

C3 Speed Bin, bez ołowiu „N” |

Kosz o wyższej prędkości |

Kosz o wyższej prędkości, wariant „N” |

Temperatura przemysłowa, ta sama gęstość |

Przemysłowy, szybsza, bez ołowiu |

EP2S60F672C4 Kroki programowania

Zanim będziesz mógł użyć FPGA EP2S60F672C4 w swoim projekcie, musisz odpowiednio skonfigurować go ze skompilowanym strumieniem bit.Proces ten polega na przygotowaniu pliku programowania, konfiguracji interfejsu sprzętowego i zapewnienia, że konfiguracja będzie prawidłowo załadować przy włączeniu.

Krok 1: Utwórz i skompiluj swój projekt

Zaczynasz od opracowania projektu logicznego za pomocą oprogramowania Intel Quartus II.Po zakończeniu projektu skompilujesz go do wygenerowania pliku programowania (.Sof lub .Pof) specjalnie dla urządzenia EP2S60F672C4.Proces kompilacji sprawdza czas, przypisania PIN i wykorzystanie zasobów, aby zapewnić, że projekt pasuje do architektury FPGA.Po skompilowaniu Twój Bitstream jest gotowy do konfiguracji urządzenia.

Krok 2: Skonfiguruj sprzęt programowy

Następnie przygotowujesz fizyczny interfejs programowania między komputerem a płytą FPGA.Zazwyczaj obejmuje to podłączenie blastera USB lub kompatybilnego kabla JTAG z portem JTAG urządzenia.Powinieneś sprawdzić, czy Quartus II rozpoznaje programista i że urządzenie docelowe jest prawidłowo wykryte.Ten krok zapewnia stabilną komunikację przed rozpoczęciem procesu konfiguracji.

Krok 3: Załaduj plik programowania do urządzenia

Korzystając z narzędzia programisty Quartus II, dodajesz skompilowany plik .sof lub .pof i wybierz ep2s60f672c4 z wykrytych listy urządzeń.Następnie inicjujesz sekwencję programowania, podczas której strumień bitów jest przenoszony i ładowany do komórek konfiguracyjnych SRAM FPGA.Powinieneś monitorować komunikaty o postępach i status, aby potwierdzić udaną konfigurację.Po zakończeniu FPGA zaczyna natychmiast wykonywać zaprogramowaną logikę.

Krok 4: Sprawdź konfigurację i działanie

Po programowaniu sprawdzasz, czy urządzenie działa zgodnie z przeznaczeniem.Quartus II zapewnia opcję weryfikacji do sprawdzenia konfiguracji CRC i sygnałów stanu, zapewniając poprawnie załadowanie projektu.Możesz także przetestować swoje funkcje we/wy lub uruchomić symulację funkcjonalną, aby potwierdzić zachowanie systemu.Ten ostatni krok zapewnia w pełni operacje i stabilne na sprzęcie.

EP2S60F672C4 Zalety i wady

Zalety

• Wysoka gęstość logiczna dla złożonych wzorów

• Dobry stosunek wydajności do kosztów

• Łatwa migracja w tej samej rodzinie

• Stabilne i dojrzałe narzędzia programistyczne

• Udowodniona niezawodność w użyciu przemysłowym

Wady

• przestarzałe i trudniejsze do pozyskiwania

• Wyższe zużycie energii niż nowsze FPGA

• Brak nowoczesnych szybkich transceiverów

• Trudniejsze zamknięcie czasu przy dużym wykorzystaniu

• Ograniczona skalowalność dla przyszłych protokołów

EP2S60F672C4 Wymiary pakowania

|

Typ |

Parametr |

|

Typ pakietu |

672-FBGA (Fineline BGA) |

|

Rozmiar ciała (L × W) |

27,00 mm × 27,00 mm |

|

Całkowita wysokość pakietu (a) |

MAX 3,50 mm |

|

Wysokość dystansu (A1) |

Min 0,30 mm |

|

Grubość podłoża (A2) |

MAX 3,00 mm |

|

Średnica kulki (B) |

0,50 mm - 0,70 mm |

|

Boisko do piłki (e) |

1,00 mm |

|

Liczba piłek |

672 |

|

Styl montażowy |

Mocowanie powierzchniowe |

|

Opis pakietu |

FBGA, siatka 27 × 27 mm |

EP2S60F672C4 Producent

EP2S60F672C4 FPGA jest wytwarzany przez Altera Corporation, wiodący pionier w programowalnych urządzeniach logicznych.W 2015 r. Altera została przejęta przez IntelA produkt jest obecnie podlegający programowalnej grupie rozwiązań Intela (PSG), która nadal wspiera i dostarcza ustalone rodziny FPGA Altera.Intel utrzymuje linię Stratix II w ramach starszego portfela produktów, zapewniając dokumentację, obsługę narzędzi i długoterminową dostępność aplikacji przemysłowych i komunikacyjnych.

Wniosek

EP2S60F672C4 łączy wysoką gęstość logiczną, elastyczną architekturę pamięci i solidne funkcje we/wy, aby obsługiwać złożone systemy cyfrowe.Projektowanie oparte na ALM, pamięć Trimatrix ™, bloki DSP i funkcje zarządzania zegarami umożliwiają wydajne wdrożenie wymagających aplikacji.Chociaż oferuje sprawdzoną niezawodność i dojrzałe wsparcie rozwojowe, stoi przed ograniczeniami, takimi jak starzenie się i brak współczesnych transceiverów w porównaniu z nowszymi pokoleniami FPGA.Ogólnie rzecz biorąc, jego zrównoważona wydajność i wszechstronność sprawiają, że jest to solidny wybór do przetwarzania sygnału, komunikacji, obsługi danych i aplikacji prototypowania.

Arkusz danych pdf

EP2S60F672C4 Arkuszy danych:

O nas

ALLELCO LIMITED

Czytaj więcej

Szybkie zapytanie.

Proszę wysłać zapytanie, natychmiast odpowiemy.

Często Zadawane Pytania [FAQ]

1. Czy EP2S60F672C4 może działać z nowoczesnymi interfejsami pamięci DDR?

Tak, obsługuje interfejsy DDR2, QDR II i RLDRAM II, które obejmują wiele wspólnych standardów pamięci zewnętrznej.To sprawia, że nadaje się do aplikacji przetwarzania danych o dużej przepustowości.

2. Czy EP2S60F672C4 wymaga specjalnego obsługi lub przechowywania?

Tak, podobnie jak inne komponenty pakowane BGA, powinny być przechowywane w opakowaniu kontrolowanym przez wilgoć i obsługiwać z ochroną ESD.Po odpowiednich praktykach przechowywania pomaga utrzymać lutowalność i niezawodność urządzenia podczas montażu.

3. Jak zmniejszyć zużycie energii w projektach EP2S60F672C4?

Możesz zoptymalizować wykorzystanie logiki, nieużywane zegary bramki, niższe napięcia we/wy, a także wykorzystać opcje syntezy zasilania w Quartus II, aby zminimalizować ogólne losowanie mocy.

4. Jakie narzędzia programowania są wymagane dla EP2S60F672C4?

Potrzebujesz oprogramowania Intel Quartus II do projektowania, kompilacji i programowania, a także kompatybilny kabel JTAG, aby skonfigurować urządzenie.

5. Czy EP2S60F672C4 obsługuje aktualizacje w polu lub zdalną rekonfigurację?

Tak, obsługuje szyfrowanie bitstreamu opartego na AES i zdalną rekonfigurację, umożliwiając bezpieczną aktualizację systemu bez fizycznego zastępowania FPGA.

Wszystko w LFXP6C-3FN256C Semiconductor kratowy

na 2025/10/6

XC2C256-7TQ144C CPLD: Pinout, funkcje, programowanie i podręcznik arkusza danych

na 2025/10/3

Popularne posty

-

Złożone komputery zestawu instrukcji: Jak zmieniły obliczenia?

na 8000/04/18 147778

-

Pinout i funkcje USB-C

na 2000/04/18 112033

-

Korzystanie z prymitywnych symulacji XILINX: kompleksowy przewodnik po projekcie i symulacji FPGA

na 1600/04/18 111352

-

Napięcia zasilania w elektronice: znaczenie VCC, VDD, VEE, VSS i GND

na 0400/04/18 83790

-

RJ45 Podręcznik złącza: pinout, okablowanie, typy kablowe i zastosowania

na 1970/01/1 79596

-

Ostateczny przewodnik po kodach kolorów drutu w nowoczesnych systemach elektrycznych

Sposób, w jaki nasze systemy elektryczne używają kolorów, nie jest tylko dla wyglądu.Każdy kolor drutu wskazuje teraz określoną funkcję, ułatwiając poprawną identyfikację komponentów elektrycznych ...na 1970/01/1 66976

-

Przewodnik zaworu oczyszczania: funkcja, objawy, testowanie i wymiana w celu optymalnej wydajności silnika

Zawór czyszczenia jest kluczową częścią systemu samochodu, który pomaga utrzymać w czystości powietrza poprzez zarządzanie oparami paliwowymi, zanim będą mogły uciec do atmosfery.To nie tylko pomag...na 1970/01/1 63110

-

Jakość (Q) Współczynnik: Równania i zastosowania

Współczynnik jakości lub „Q” jest ważny podczas sprawdzania, jak dobrze induktory i rezonatory działają w systemach elektronicznych, które wykorzystują częstotliwości radiowe (RF).„Q” mierzy, jak d...na 1970/01/1 63043

-

Osiągnięcie wydajności szczytowej przy maksymalnym twierdzeniu o przeniesieniu mocy

Twierdzenie o maksymalnym przeniesieniu mocy wyjaśnia, w jaki sposób energia ze źródła, takiego jak akumulator lub generator, płynie do podłączonego obciążenia.Pokazuje dokładny warunek, w którym o...na 1970/01/1 54097

-

A23 Specyfikacje i kompatybilność baterii

Akumulator A23 to mała akumulator w kształcie cylindra o wysokim napięciu.Nazywany również 23a, 23E lub Mn21, działa przy 12 woltach i znacznie wyższy niż akumulatory AA lub AAA.Jego specj...na 1970/01/1 52197