EP1C4F400C8 FPGA: Funkcje, specyfikacje, programowanie i alternatywy

Jeśli pracujesz z programowalną logiką, EP1C4F400C8 zapewnia praktyczną równowagę wydajności i kosztów.W tym artykule dowiesz się, jaki jest ten FPGA, jego kluczowe funkcje, takie jak pojemność logiczna, pamięć i opcje we/wy, oraz jak jego struktura obsługuje niezawodny projekt.Zobaczysz także jego specyfikacje, aplikacje w systemach, proces programowania i sposób, w jaki porównuje się z podobnymi częściami.Katalog

Co to jest EP1C4F400C8?

. EP1C4F400C8 jest członkiem rodziny cyklonu FPGA Intel (wcześniej Altera), zaprojektowanej jako opłacalne i niezawodne programowalne rozwiązanie logiczne.To urządzenie, zbudowane na procesie SRAM 0,13 µM, oferuje umiarkowaną gęstość logiczną i elastyczne opcje we/wy w kompaktowym pakiecie FBGA-400.Rodzina cyklonu, która obejmuje urządzenia takie jak EP1C3, EP1C6, EP1C12 i EP1C20, została stworzona w celu zrównoważenia wydajności i przystępności cenowej dla skalowalnych projektów, umożliwiając łatwą migrację między poziomami gęstości i pakietów.Znany ze stabilności i szerokiego adopcji, pozostaje zaufanym wyborem w starszych projektach.

Szukasz EP1C4F400C8?Skontaktuj się z nami, aby sprawdzić aktualne zapasy, czas realizacji i ceny.

Modele CAD EP1C4F400C8

Symbol EP1C4F400C8

Ślad EP1C4F400C8

Model 3D EP1C4F400C8

Funkcje EP1C4F400C8

• • Pojemność logiczna

EP1C4F400C8 oferuje około 4000 elementów logicznych, zorganizowanych w 400 blokach macierzy logicznej (laboratoria).To sprawia, że nadaje się do projektów średniego zasięgu, które wymagają umiarkowanej gęstości logicznej przy jednoczesnym zachowaniu wydajności kosztowej.

• • Wbudowana pamięć

Integruje około 76,5 kBits wbudowanej pamięci.Ten wewnętrzny pamięć RAM obsługuje funkcje buforowania danych, przechowywania i małych pamięci, zmniejszając potrzebę zewnętrznych komponentów pamięci w wielu projektach.

• • Wysoka liczba we/wy

Urządzenie zapewnia 301 styków we/wy-konfiguracyjnych użytkowników w pakiecie 400-balowym FBGA.Ta wysoka liczba pinów umożliwia bogatą łączność dla złożonych systemów wymagających wielu interfejsów obwodowych.

• • Szerokie wsparcie standardów we/wy

Obsługuje wiele standardów we/wy, w tym LVTTL, LVCMOS, SSTL-2, SSTL-3 i różnicowe LVD.Ta elastyczność pozwala FPGA bezpośrednio łączyć się z różnymi nowoczesnymi rodzinami logicznymi i urządzeniami pamięci.

• • Szybkie sygnalizacja różnicowa

Dzięki obsłudze LVDS do 640 Mb / s, FPGA obsługuje szybkie wymagania dotyczące transferu danych.To sprawia, że jest to praktyczne dla aplikacji, takie jak szybkie linki komunikacyjne i szybkie interfejsy cyfrowe.

• • Zarządzanie zegarami z PLLS

Chip integruje dwie fazowe pętle (PLLS) i osiem globalnych sieci zegarowych.Funkcje te umożliwiają precyzyjne wytwarzanie zegara, mnożenie i kontrolę jittera dla zastosowań krytycznych czasowych.

• • Operacja rdzenia niskiego napięcia

Działając na nominalnym napięciu rdzenia 1,5 V, urządzenie równoważy wydajność przy niższym zużyciu energii.Ten poziom napięcia został zoptymalizowany pod kątem technologii CMOS 0,13 µm zastosowanej w jej wytwarzaniu.

• • Elastyczne napięcia we/wy

FPGA obsługuje napięcia we/wy 1,5 V, 1,8 V, 2,5 V i 3,3 V w różnych bankach.Ta wszechstronność umożliwia interfejs zarówno z starszymi, jak i nowoczesnymi komponentami systemowymi.

• • Konfiguracja oparta na SRAM

Podobnie jak inne Cyklonowe FPGA, jest oparty na SRAM i wymaga rekonfiguracji przy każdym ulepszeniu.Zapewnia to elastyczność aktualizacji, ale wymaga również zewnętrznego urządzenia lub kontrolera konfiguracyjnego.

• • Obsługa kompresji Bitstream

EP1C4F400C8 obsługuje ładowanie sprężonego strumienia bitów podczas konfiguracji.Zmniejsza to wymagania pamięci zewnętrznej i przyspiesza czas konfiguracji.

• • Zgodność z PCI

Zawiera wbudowaną obsługę standardów PCI (33/66 MHz, 32/64-bit).Ta funkcja umożliwia bezpośrednio integrację urządzenia z systemami wymagającymi interfejsu PCI bez dodatkowej logiki mostkowania.

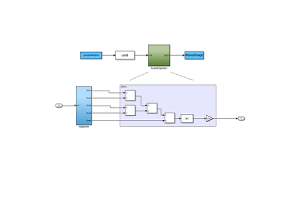

Struktura laboratoryjna cyklonu

Schemat pokazuje strukturę tablicy logicznej (laboratorium) stosowaną w cyklonowych FPGA, takich jak EP1C4F400C8.Każde laboratorium łączy się z siecią połączeń: połączenia wiersza, połączenia kolumnowe i lokalne połączenia, które prowadzą sygnały między elementami logicznymi a innymi blokami.Bezpośrednie połączenia łączące zapewniają szybkie, niskie ścieżki opóźnienia do sąsiednich laboratoriów, poprawiając wydajność czasu na ścieżkach sygnałowych.Ta architektura jest ważna, ponieważ równoważy elastyczność routingu z wydajnością, umożliwiając FPGA obsługę złożonych projektów przy jednoczesnym utrzymaniu optymalizacji prędkości i obszaru.

Schemat banków I/O cyklon

Schemat ilustruje strukturę banków we/wy cyklonu FPGA, takie jak EP1C4F400C8.Urządzenie jest podzielone na cztery banki we/wy, z których każdy zasilał własną magistralę zaopatrzenia, umożliwiając mieszanie różnych standardów napięcia w ramach jednego FPGA.Wszystkie banki obsługują szeroki zakres standardów we/wy, w tym LVTTL, LVCMOS, LVDS, RSDS i SSTL, podczas gdy banki 1 i 3 również obsługują 3,3-V PCI dla kompatybilności ze starszymi systemami.Ta elastyczna architektura we/wy jest ważna, ponieważ umożliwia bezproblemową integrację z różnorodnymi urządzeniami zewnętrznymi i interfejsami, dzięki czemu FPGA jest dostosowywana do różnych aplikacji.

Specyfikacje EP1C4F400C8

|

Typ |

Parametr |

|

Producent |

Altera/Intel |

|

Szereg |

Cyclone® |

|

Opakowanie |

Taca |

|

Status części |

Przestarzały |

|

Liczba laboratoriów/CLB |

400 |

|

Liczba elementów/komórek logicznych |

4000 |

|

Całkowite bity RAM |

78 336 |

|

Liczba we/wy |

301 |

|

Napięcie - zasilanie |

1,425 V ~ 1,575 V. |

|

Typ montażu |

Mocowanie powierzchniowe |

|

Temperatura robocza |

0 ° C ~ 85 ° C (TJ) |

|

Pakiet / obudowa |

400-BGA |

|

Pakiet urządzeń dostawcy |

400-FBGA (21 × 21) |

|

Podstawowy numer produktu |

EP1C4 |

Aplikacje EP1C4F400C8

1. Cyfrowe przetwarzanie sygnału (DSP)

EP1C4F400C8 można zaprogramować do wykonywania zadań takich jak filtrowanie, FFT i modulacja sygnału.Jego połączenie elementów logicznych i wbudowanej pamięci sprawia, że nadaje się do szybkiego przetwarzania.Pozwala to na zastąpienie tradycyjnych układów DSP elastycznym rozwiązaniem FPGA, które można przeprogramować dla różnych algorytmów.

2. Systemy osadzone i sterujące

W systemach przemysłowych i wbudowanych ta FPGA jest często używana do wdrażania niestandardowych kontrolerów, sekwencerów i maszyn stanowych.Jego rekonfigurowalna logika pozwala dokładnie dostosowywać zachowanie sprzętowe do potrzeb systemowych.Dzięki zintegrowaniu logiki kontroli wewnątrz FPGA liczba komponentów zewnętrznych jest zmniejszona, poprawiając niezawodność i obniżenie kosztów.

3. Mostkowanie komunikacji i interfejsu

Urządzenie obsługuje wiele standardów we/wy i może działać jako pomost między różnymi protokołami komunikacji.Jest często używany do płynnego łączenia PCI, LVDS, SDRAM i innych interfejsów w systemie.To sprawia, że jest bardzo przydatny w urządzeniach sieciowych, wbudowanych kontrolerach i starszych konwersjach interfejsu.

4. Akwizycja i przetwarzanie danych

Przy wysokiej dostępności we/wy i elastycznej pamięci EP1C4F400C8 jest dobrze odpowiednie dla systemów gromadzenia danych.Może bezpośrednio współpracować z ADC i czujnikami, przetwarzać dane w czasie i przygotowywać je do przechowywania lub transmisji.Takie zastosowania są powszechne w instrumentach medycznych, urządzeniach testowych i naukowych urządzeniach pomiarowych.

EP1C4F400C8 Podobne części

|

Specyfikacja |

EP1C4F400C8 |

EP1C4F400C8N |

EP1C4F400C8NAA |

EP1C4F400C6N |

EP1C4F324C8N |

EP1C4T144C8N |

|

Producent |

Altera (Intel) |

Altera (Intel) |

Altera (Intel) |

Altera (Intel) |

Altera (Intel) |

Altera (Intel) |

|

Rodzina FPGA |

Cyklon (EP1C4) |

Cyklon (EP1C4) |

Cyklon (EP1C4) |

Cyklon (EP1C4) |

Cyklon (EP1C4) |

Cyklon (EP1C4) |

|

Elementy logiczne (LES) |

4000 |

4000 |

4000 |

4000 |

4000 |

4000 |

|

Wbudowana pamięć (bity) |

~ 76,5 KBITS |

~ 76,5 KBITS |

~ 76,5 KBITS |

~ 76,5 KBITS |

~ 76,5 KBITS |

~ 76,5 KBITS |

|

Piny we/wy |

301 |

301 |

301 |

301 |

249 |

97 |

|

Pakiet / obudowa |

400-FBGA |

400-FBGA |

400-FBGA |

400-FBGA |

324-FBGA |

144-TQFP |

|

Stopień prędkości |

C8 |

C8 |

C8 |

C6 (szybciej) |

C8 |

C8 |

|

Napięcie rdzenia |

1,5 v |

1,5 v |

1,5 v |

1,5 v |

1,5 v |

1,5 v |

|

Temperatura operacyjna.Zakres |

0 ° C ~ 85 ° C. |

0 ° C ~ 85 ° C. |

0 ° C ~ 85 ° C. |

0 ° C ~ 85 ° C. |

0 ° C ~ 85 ° C. |

0 ° C ~ 85 ° C.

|

EP1C4F400C8 Kroki programowania

Zanim będziesz mógł użyć FPGA EP1C4F400C8, musisz załadować swój projekt do urządzenia.Programowanie polega na konfigurowaniu FPGA z plikami Stream, aby wiedział, jak zachowywać się jako zamierzony obwód.

1. Wybierz Schemat konfiguracji i ustaw piny MSEL

Zaczynasz od wybrania schematu konfiguracji, który najlepiej pasuje do Twojej konfiguracji, takiej jak aktywny serial, pasywny serial lub JTAG.Odbywa się to poprzez ustawienie pinów MSEL na określone poziomy logiki przed ulepszeniem.Każdy tryb używa różnych pinów i protokołów, więc musisz potwierdzić kompatybilność z narzędziami projektowymi i pamięcią konfiguracji.Dokonanie właściwego wyboru zapewnia płynny proces konfiguracji.

2. Zastosuj zasilanie i zainicjuj urządzenie

Następnie włącz szyny rdzenia FPGA i we/wy w określonych zakresach napięcia.Podczas uruchamiania trzymaj pin NCONFIG niski, aby utrzymać urządzenie w resetowaniu, aż napięcia zasilania będą stabilne.Po stabilności zwolniasz reset, a urządzenie sygnalizuje gotowość, kierując pinem NSTATUS.Gwarantuje to, że FPGA jest prawidłowo inicjowana przed rozpoczęciem konfiguracji.

3. Przekazuj konfigurację Bitstream

Na tym etapie wysyłasz plik danych konfiguracyjnych (BitStream) do FPGA za pomocą wybranego schematu.W aktywnym trybie szeregowym lub pasywnym Bitstream pochodzi z zewnętrznego urządzenia pamięci, a JTAG umożliwia bezpośrednie programowanie za pomocą kabla.Urządzenie ciągle odczytuje dane konfiguracyjne do momentu zakończenia.Twoje oprogramowanie projektowe generuje ten strumień bitów, aby pasowały do twoich wymagań logicznych.

4. Potwierdź udaną konfigurację (conf_done)

Kiedy FPGA kończy ładowanie, potwierdza pin CONF_DONE, aby pokazać, że dane konfiguracyjne zostały pomyślnie odebrane.Jednocześnie urządzenie wykonuje wewnętrzną inicjalizację, taką jak rejestry usuwania i aktywacja we/wy.Jeśli conf_done nie wzrośnie wysoko, zwykle oznacza to, że dane konfiguracyjne lub konfiguracja mają błąd.Oglądanie tego PIN jest najprostszym sposobem weryfikacji procesu, jest zakończone.

5. Wykonaj opcjonalną rekonfigurację systemu

Na koniec masz opcję aktualizacji lub przeprogramowania FPGA bez usuwania go z płyty.Za pomocą JTAG lub kontrolera wbudowanego możesz bezpośrednio załadować nowy strumień bitów, co jest przydatne do aktualizacji oprogramowania układowego.Ta elastyczność pozwala na modyfikację, debugowanie lub aktualizację systemu nawet po wdrożeniu.Zapewnia, że projekt oparty na FPGA może z czasem dostosować się do zmieniających się wymagań.

EP1C4F400C8 Zalety i wady

Zalety

• Opłacalny wybór dla wzorów średniego zasięgu

• Wysoka liczba we/wy w porównaniu do urządzeń o podobnej gęstości

• Elastyczne napięcie i standardowe wsparcie we/wy

• Wspierane przez dojrzałe narzędzia i dokumentację

• Niższe zużycie mocy niż starsze generacje FPGA

Wady

• przestarzały z ograniczoną długoterminową dostępnością

• Niższa pojemność logiki i pamięci vs. nowoczesne FPGA

• Wolniejsza prędkość robocza i wydajność we/wy

• Wymaga pamięci zewnętrznej do konfiguracji po włączeniu

• Brak zaawansowanych funkcji, takich jak bloki DSP i szybkie transceiver

EP1C4F400C8 Wymiary pakowania

|

Typ |

Parametr |

|

Typ pakietu |

FBGA (tablica siatki kulkowej) |

|

Liczba piłki |

400 |

|

Boisko do piłki (e) |

1,0 mm (typowe dla cyklonu EP1C4F400) |

|

Średnica kulki (B) |

0,45 mm (nominalne) |

|

Rozmiar pakietu (D × E) |

21 mm × 21 mm |

|

Wysokość pakietu (a) |

2,40 mm (maks.) |

|

Grubość podłoża (A2) |

~ 0,40 mm |

|

Grubość czapki pleśni (A3) |

~ 1,90 mm |

|

Wysokość piłki (A1) |

0,25 mm (nominalne) |

|

Pin A1 Corner |

Oznaczony do orientacji |

|

Układ tablicy |

Grid 20 × 20 (z brakującymi kulkami narożnymi) |

|

Montowanie |

Mocowanie powierzchniowe (SMD) |

EP1C4F400C8 Producent

EP1C4F400C8 został pierwotnie wyprodukowany przez Altera Corporation, pionier w programowalnych urządzeniach logicznych i technologii FPGA.W 2015 r. Altera została przejęta przez Intel Corporation, a linia produktu stała się częścią programu programowalnych rozwiązań Intel (PSG).Dzisiaj Intel obsługuje te starsze urządzenia Altera, jednocześnie koncentrując rozwój na nowszych rodzinach FPGA, zapewniając ciągłość istniejącym użytkownikom i rozwijając innowacje w programowalnej logice.

Wniosek

EP1C4F400C8 wyróżnia się jako opłacalna i wszechstronna FPGA, która oferuje solidną wydajność dla projektów średniego zasięgu.Dzięki 4000 elementom logicznym, wbudowanej pamięci, obszernej obsługi we/wy i kompatybilności z wieloma standardami napięcia i interfejsu zapewnia elastyczność w różnych aplikacjach.Jego architektura, proces programowania i szeroka użyteczność w DSP, systemach wbudowanych i pozyskiwanie danych sprawiają, że jest to praktyczny wybór pomimo starszego statusu.Chociaż brakuje mu zaawansowanych funkcji znalezionych w nowszych urządzeniach i stoi w obliczu ograniczonej długoterminowej dostępności, pozostaje niezawodną opcją poszukującą sprawdzonych rozwiązań w skalowalnych projektach FPGA.

Arkusz danych pdf

Arkusze danych EP1C4F400C8:

O nas

ALLELCO LIMITED

Czytaj więcej

Szybkie zapytanie.

Proszę wysłać zapytanie, natychmiast odpowiemy.

Często Zadawane Pytania [FAQ]

1. Jakie narzędzia są wymagane do zaprogramowania EP1C4F400C8?

Potrzebujesz oprogramowania Intel Quartus (wcześniej Altera Quartus II) wraz z obsługiwanym kablem programistycznym, takim jak Blaster USB.Te narzędzia pozwalają utworzyć strumień bitów i ładowanie go do FPGA.

2. Czy EP1C4F400C8 może bezpośrednio obsługiwać aplikacje PCI?

Tak, ma wbudowaną zgodność ze standardami PCI (33/66 MHz, 32/64-bit), co czyni go odpowiednim do integracji systemu opartego na PCI bez wymagania dodatkowej logiki mostkowania.

3. Co się stanie, jeśli EP1C4F400C8 zawiedzie podczas konfiguracji?

Jeśli konfiguracja się nie powiedzie, pin CONF_DONE nie zapewni wysoko.Zazwyczaj wskazuje to na błąd w pliku Bitstream, sekwencjonowaniu napięcia lub konfiguracji pinu i powinno być ponownie sprawdzone w przepływie projektu.

4. Czy interfejs EP1C4F400C8 może bezpośrednio z pamięcią DDR?

Obsługuje kilka standardów we/wy, ale nie ma natywnych interfejsów DDR, takich jak nowoczesne FPGA.Mogą być potrzebne dodatkowe względy projektowe lub komponenty pomostowe.

5. W jaki sposób EP1C4F400C8 porównuje się do nowszych FPGA?

W porównaniu z nowoczesnymi urządzeniami EP1C4F400C8 ma niższą prędkość, mniej gęstości logicznej i mniej zaawansowanych funkcji.Pozostaje jednak opłacalnym wyborem stabilnych, średniego zasięgu, w których najnowocześniejsza wydajność nie jest wymagana.

EPM3256AFC256-7 CPLD Omówienie: Funkcje, pinout, programowanie i aplikacje

na 2025/10/3

Analog432BR Analog Switch IC: Specyfikacje, pinout, alternatywy i arkusz danych

na 2025/10/2

Popularne posty

-

Złożone komputery zestawu instrukcji: Jak zmieniły obliczenia?

na 8000/04/18 147778

-

Pinout i funkcje USB-C

na 2000/04/18 112038

-

Korzystanie z prymitywnych symulacji XILINX: kompleksowy przewodnik po projekcie i symulacji FPGA

na 1600/04/18 111352

-

Napięcia zasilania w elektronice: znaczenie VCC, VDD, VEE, VSS i GND

na 0400/04/18 83795

-

RJ45 Podręcznik złącza: pinout, okablowanie, typy kablowe i zastosowania

na 1970/01/1 79602

-

Ostateczny przewodnik po kodach kolorów drutu w nowoczesnych systemach elektrycznych

Sposób, w jaki nasze systemy elektryczne używają kolorów, nie jest tylko dla wyglądu.Każdy kolor drutu wskazuje teraz określoną funkcję, ułatwiając poprawną identyfikację komponentów elektrycznych ...na 1970/01/1 66978

-

Przewodnik zaworu oczyszczania: funkcja, objawy, testowanie i wymiana w celu optymalnej wydajności silnika

Zawór czyszczenia jest kluczową częścią systemu samochodu, który pomaga utrzymać w czystości powietrza poprzez zarządzanie oparami paliwowymi, zanim będą mogły uciec do atmosfery.To nie tylko pomag...na 1970/01/1 63113

-

Jakość (Q) Współczynnik: Równania i zastosowania

Współczynnik jakości lub „Q” jest ważny podczas sprawdzania, jak dobrze induktory i rezonatory działają w systemach elektronicznych, które wykorzystują częstotliwości radiowe (RF).„Q” mierzy, jak d...na 1970/01/1 63045

-

Osiągnięcie wydajności szczytowej przy maksymalnym twierdzeniu o przeniesieniu mocy

Twierdzenie o maksymalnym przeniesieniu mocy wyjaśnia, w jaki sposób energia ze źródła, takiego jak akumulator lub generator, płynie do podłączonego obciążenia.Pokazuje dokładny warunek, w którym o...na 1970/01/1 54097

-

A23 Specyfikacje i kompatybilność baterii

Akumulator A23 to mała akumulator w kształcie cylindra o wysokim napięciu.Nazywany również 23a, 23E lub Mn21, działa przy 12 woltach i znacznie wyższy niż akumulatory AA lub AAA.Jego specj...na 1970/01/1 52198