EP1C4F324C7N FPGA: Arkusz danych, funkcje, programowanie i specyfikacje

Ten przewodnik dotyczy EP1C4F324C7N, rodzaju układu FPGA wykonanego przez Intel.Jest świetny dla projektów, które wymagają dobrej wydajności, ale także muszą pozostać w ramach budżetu.W tym artykule dowiesz się, co może zrobić ten układ, jak działa, gdzie jest używany i jak go zaprogramować.Niezależnie od tego, czy pracujesz nad elektroniką dla samochodów, fabryk, a nawet urządzeń domowych, ten przewodnik pomoże ci zrozumieć, dlaczego EP1C4F324C7N jest inteligentnym i elastycznym wyborem.Katalog

Przegląd EP1C4F324C7N

. EP1C4F324C7N jest częścią serii Intel Cyclone® FPGA, specjalnie zaprojektowanej do opłacalnych zastosowań wymagających dobrego równowagi wydajności i niskich kosztów.Ta FPGA ma 4000 elementów logicznych i 400 bloków macierzy logicznych (LABS), zapewniając solidne możliwości umiarkowanych projektów złożoności.Obejmuje 76,5 kilobit całkowitego pamięci RAM i obsługuje do 249 pinów we/wy, co czyni go wysoce wszechstronnym dla różnych wymagań interfejsu.Działając na częstotliwościach do 320 MHz i przy zakresie napięcia zasilania od 1,425 V do 1,575 V, EP1C4F324C7N jest przygotowany do obsługi wymagających aplikacji.Obsługuje szeroką gamę standardów we/wy, takich jak LVTTL, LVCMOS, SSTL-2 i SSTL-3, i jest kompatybilny z zewnętrznymi typami pamięci, takimi jak DDR SDram, zwiększając jego użyteczność w cyfrowym przetwarzaniu sygnałów, wbudowane systemy obliczeniowe i automatyzacyjne.

Jeśli chcesz sprawić, aby Twoja operacja działała płynnie z niezawodną technologią, złożenie z nas masowej kolejności tej FPGA może pomóc w zapewnieniu dostępności i spójności potrzebnych do swoich projektów.

Modele CAD EP1C4F324C7N

Symbol EP1C4F324C7N

EP1C4F324C7N Stopprint

Model 3D EP1C4F324C7N

Funkcje EP1C4F324C7N

• • Elementy logiczne: FPGA zawiera 4000 elementów logicznych, które umożliwiają efektywne wdrożenie złożonych obwodów logicznych i funkcji cyfrowych.

• • Bloki tablicy logicznej (laboratoria): Obejmuje 400 laboratoriów, które są podstawowymi elementami składowymi dla architektury FPGA, ułatwiając projektowanie wszechstronnych konfiguracji logiki cyfrowej.

• • Całkowite bity RAM: FPGA jest wyposażony w 76,5 kilobit wbudowanego pamięci RAM, zapewniając zasoby pamięci na chipie do szybkiego przetwarzania danych i przechowywania danych.

• • Liczba pinów we/wy: Przy 249 pinach I/O-konfiguracyjnych użytkownika EP1C4F324C7N obsługuje szeroki zakres opcji interfejsu, dostosowując się do różnych standardów sygnałów i komponentów elektronicznych.

• • Częstotliwość robocza: Może działać przy częstotliwościach do 320 MHz, umożliwiając efektywne obsługę szybkich zadań obliczeniowych i procesów.

• • Napięcie zasilania: Urządzenie działa w zakresie napięcia zasilania od 1,425 V do 1,575 V, zapewniając elastyczne i niezawodne zarządzanie energią w różnych zastosowaniach.

• • Pętle z blokadem fazowym (PLLS): Zawiera pętle z blokadą faz dla precyzyjnego zarządzania zegara do zastosowań wrażliwych na rozrząd.

• • Obsługa wielu standardów we/wy: FPGA obsługuje różne standardy we/wy, takie jak LVTTL, LVCMOS, SSTL-2 i SSTL-3, co zwiększa jego zgodność z szerokim zakresem komponentów i systemów elektronicznych.

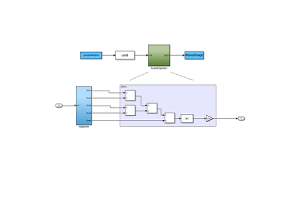

Schemat blokowy EP1C4F324C7N

Schemat ilustruje strukturę połączeń w ramach FPGA, w szczególności odwołując się do EP1C4F324C7N Urządzenie z serii Cyklonu Altera.U podstaw tego układu są Bloki tablicy logicznej (Labs), które są modułami wyrównanymi pionowo, które zawierają klastry elementów logicznych odpowiedzialnych za wdrażanie funkcji logiki użytkownika.Każde laboratorium jest podłączone do sąsiednich laboratoriów poprzez bezpośrednie połączenia linków, umożliwiając szybką komunikację i minimalizowanie opóźnień propagacji sygnału.Te bezpośrednie linki zapewniają wydajny, zlokalizowany transfer danych między sąsiednimi blokami logicznymi bez konsumpcji szerszych zasobów routingu.

Otaczają się dwa podstawowe typy globalnych połączeń: Row interconnects I Kolumna połączeń.Te szerokie niebieskie linie służą jako autostrady routingowe, umożliwiając sygnały przemierzanie większych odcinków tkaniny FPGA.Rządowe połączenia występują poziomo, podczas gdy kolumna wzajemnie łączy się pionowo.Ułatwiają połączenie między odległymi blokami logicznymi a interfejsem z elementami wejściowymi/wyjściowymi lub innymi jednostkami funkcjonalnymi umieszczonymi na układie.

Lokalny interkonekt znajduje się między laboratoriami i służy jako materiał przełączający, który łączy globalne połączenia z laboratoriami.Umożliwia blokom logicznym dostęp do sygnałów zarówno z bezpośrednich, jak i globalnych połączeń.Ta hierarchia routingu, łącząca ścieżki bezpośrednie, lokalne, wierszowe i kolumnowe, zapewnia elastyczne i skalowalne podejście do rozkładu sygnału, optymalizując wydajność i wykorzystanie logiki w ramach FPGA EP1C4F324C7N.

EP1C4F324C7N Specyfikacje

|

Typ |

Parametr |

|

Producent |

Altera/Intel |

|

Szereg |

Cyclone® |

|

Opakowanie |

Taca |

|

Status części |

Przestarzały |

|

Liczba laboratoriów/CLB |

400 |

|

Liczba elementów/komórek logicznych |

4000 |

|

Całkowite bity RAM |

78 336 |

|

Liczba we/wy |

249 |

|

Napięcie - zasilanie |

1,425 V ~ 1,575 V. |

|

Typ montażu |

Mocowanie powierzchniowe |

|

Temperatura robocza |

0 ° C ~ 85 ° C (TJ) |

|

Pakiet / obudowa |

324-BGA |

|

Pakiet urządzeń dostawcy |

324-FBGA (19x19) |

|

Podstawowy numer produktu |

EP1C4 |

EP1C4F324C7N Zastosowania

Sprzęt sieciowy

EP1C4F324C7N jest wysoce odpowiedni do użytku w urządzeniach sieciowych, takich jak przełączniki, routery i modemy.Pomaga skutecznie zarządzać ruchem danych, poprawia przepustowość i zmniejszając opóźnienie w celu utrzymania wysokowydajnych operacji sieciowych.

Automatyzacja przemysłowa

W dziedzinie automatyzacji przemysłowej ta FPGA może być używana do sterowania maszynami i systemami robotycznymi.Jego zdolność do szybkiego przetwarzania złożonych algorytmów pozwala na kontrolę i monitorowanie, zwiększenie wydajności i bezpieczeństwa w środowiskach produkcyjnych.

Elektronika konsumpcyjna

EP1C4F324C7N znajduje aplikacje w elektronice użytkowej, szczególnie w prowadzeniu wyświetlaczy o wysokiej rozdzielczości i zarządzaniu interaktywnymi interfejsami w urządzeniach takich jak telewizory inteligentne i zaawansowane systemy automatyzacji domów.Jego solidne możliwości przetwarzania zapewniają płynne i responsywne doświadczenia.

Systemy motoryzacyjne

W aplikacjach motoryzacyjnych ta FPGA przyczynia się do funkcjonalności zaawansowanych systemów wspomagania sterownika (ADAS) i systemów rozrywkowych w pojazdach.Wspiera przetwarzanie i podejmowanie decyzji w zakresie funkcji bezpieczeństwa i rozrywki w nowoczesnych pojazdach.

Lotnisko i obrona

FPGA ma również zastosowanie w sektorach lotniczych i obronnych, gdzie obsługuje zadania przetwarzania sygnału i obrazu dla systemów radarowych i komunikacyjnych.Jego wysoka niezawodność i zdolność do działania w ekstremalnych warunkach sprawiają, że jest idealny do zastosowań wojskowych i lotniczych.

EP1C4F324C7N Podobne części

• • EP1C4F324C8N

• • EP1C4F324I7N

• • EP1C4F324C8

EP1C4F324C7N Kroki programowania

1. Tworzenie projektowania: Zacznij od napisania projektu przy użyciu języka opisu sprzętu, takiego jak VHDL lub Verilog.Ten kod określa strukturę logiczną i funkcję implementacji sprzętowej.Ważne jest, aby dokładnie przetłumaczyć pomysł na sprzęt na HDL, aby zapewnić, że FPGA zachowuje się zgodnie z oczekiwaniami.Przed przejściem do implementacji sprzętu symuluj kod HDL za pomocą oprogramowania symulacyjnego.Ten krok testuje logikę i funkcjonalność twojego projektu w środowisku wirtualnym, umożliwiając identyfikację i naprawienie błędów na początku procesu rozwoju.

2. Kompilacja i synteza : Użyj oprogramowania Quartus II Altera, aby skompilować i syntetyzować kod HDL.Kompilacja przekłada Twój HDL na listę netto, ogólny opis sprzętu FPGA, który mapuje Twój projekt na elementy logiczne i zasoby routingu.Proces dopasowania, częścią przepływu pracy Quartus II, polega na umieszczeniu i kierowaniu projektu w FPGA.Optymalizuje umieszczenie elementów logicznych i routing połączeń w celu spełnienia wymagań dotyczących wydajności i minimalizacji wykorzystania zasobów.

3. Przypisanie PIN: Plannik PIN w Quartus II umożliwia przypisanie określonych pinów na FPGA do wejść i wyjść zdefiniowanych w kodzie HDL.Właściwe przypisanie PIN jest dobre do fizycznego połączenia i interakcji FPGA z innymi komponentami sprzętowymi w twoim systemie.

4. Analiza czasu: Użyj analizatora czasu Quest Quest, aby upewnić się, że Twój projekt spełnia wymagania dotyczące pomiaru czasu.To narzędzie sprawdza czas konfiguracji i trzymania oraz ogólną wydajność czasu, pomagając zapobiegać takimi problemami, jak uszkodzenie danych i niestabilność systemu.

5. Generowanie plików programowania: Po skompilowaniu projektu, zsyntetyzowaniu i weryfikowanym do czasu, użyj narzędzia asemblera w Quartus II, aby wygenerować plik programowania.Ten plik, zwykle z rozszerzeniem .sof (plik obiektu SRAM) lub .POF (programowalny plik obiektu), zawiera dane konfiguracyjne dla FPGA.

6. Programowanie urządzeń: Podłącz płytę FPGA do komputera za pomocą interfejsu JTAG, takiego jak Blaster USB.Ten interfejs służy do przesyłania pliku programowania z komputera do FPGA.Otwórz narzędzie programisty Quartus II, aby załadować i przenieść plik programowania do FPGA.Ten krok konfiguruje FPGA z twoim projektem, zasadniczo „programowanie” urządzenia do wykonywania pożądanych funkcji.

7. Weryfikacja: Po zaprogramowaniu FPGA wykonaj testy funkcjonalne, aby sprawdzić, czy FPGA działa poprawnie zgodnie ze specyfikacjami projektowymi.Testowanie to może obejmować uruchamianie przypadków testowych w środowisku laboratoryjnym, sprawdzanie operacji interfejsu i zapewnienie prawidłowej interakcji FPGA z innymi komponentami sprzętowymi.

EP1C4F324C7N Zalety

Elastyczność i rekonfiguracja

EP1C4F324C7N oferuje niezrównaną elastyczność w porównaniu do mikrokontrolerów i ASIC, które są ustalone w ich funkcji po wyprodukowaniu.To FPGA można przeprogramować, aby dostosować się do nowych wymagań lub zmian w projektowaniu systemu dla aplikacji, które ewoluują w czasie.Ta rekonfigurację pozwala aktualizować swoje systemy bez wymiany sprzętu, skracanie czasu i czasu rozwoju.

Możliwości przetwarzania równoległego

Dzięki jego zdolności do wykonywania wielu operacji jednocześnie EP1C4F324C7N wyróżnia się w środowiskach wymagających obliczeń o wysokiej wydajności.Ta zdolność przetwarzania równoległego jest zaletą w stosunku do tradycyjnych mikrokontrolerów, które działają sekwencyjnie, dzięki czemu FPGA jest bardziej odpowiednia do intensywnych aplikacji, takich jak cyfrowe przetwarzanie sygnałów, przetwarzanie wideo i złożone systemy sterowania.

Niestandardowa implementacja sprzętu

FPGA pozwala na zaprojektowanie niestandardowej logiki sprzętowej dostosowanej specjalnie do potrzeb operacyjnych użytkownika.Oznacza to, że EP1C4F324C7N można zoptymalizować do wykonywania określonych zadań bardziej wydajnie niż standardowe procesory lub ASIC, zapewniając doskonałą wydajność i wydajność energetyczną dla wyspecjalizowanych aplikacji.

Opłacalność dla produkcji o niskiej i średniej objętości

W przypadku projektów, w których ilości produkcji nie uzasadniają wysokich kosztów rozwoju ASIC, EP1C4F324C7N stanowi opłacalną alternatywę.Zapewnia zalety niestandardowego sprzętu bez znacznych inwestycji z góry wymaganych do projektowania i produkcji ASIC, co czyni go idealnym do prototypów, małych i średnich projektów lub wyspecjalizowanych zastosowań przemysłowych.

Integracja i efektywność przestrzeni

Możliwość integracji wielu funkcji i komponentów z pojedynczym układem FPGA sprawia, że EP1C4F324C7N jest bardzo cenny w zastosowaniach ograniczonych kosmicznych.Ta integracja prowadzi do mniejszych, bardziej kompaktowych projektów urządzeń, świetnych w przenośnej elektronice, aplikacjach samochodowych i innych scenariuszach, w których potrzebna jest wydajność przestrzeni.

EP1C4F324C7N Wymiary pakowania

• • Typ pakietu: 324-pinowy zestaw siatki kulkowej (FBGA)

• • Rozmiar pakietu (Długość x szerokość): 19 mm x 19 mm

• • Maksymalna wysokość siedzenia: 3,5 mm

• • Boisko terminala: 1 mm

EP1C4F324C7N Producent

EP1C4F324C7N to tablica bramy programowalnej (FPGA) produkowana przez Intel, po ich nabyciu altera.W ramach serii Intel Cyclone® ten FPGA reprezentuje segment szerokiego portfela Intela zintegrowanych rozwiązań technologicznych.Intel, lider w branży półprzewodnikowej, integruje zaawansowane technologie produkcyjne i szerokie wsparcie w celu zapewnienia solidnych rozwiązań FPGA, w tym EP1C4F324C7N, która ma złożone możliwości logiczne w kompaktowej formie.Ta FPGA podkreśla zaangażowanie Intela w dostarczanie wysokowydajnych komponentów obliczeniowych, które zaspokajają różnorodne potrzeby technologiczne.

Wniosek

Niezależnie od tego, czy opracowujesz niestandardową logikę sterowania, budowanie szybkich systemów komunikacyjnych, czy prototypowanie specjalistycznych funkcji cyfrowych, FPGA EP1C4F324C7N zapewnia optymalną równowagę wydajności, elastyczności i kosztów.Dzięki szerokiej kompatybilności we/wy, zintegrowanej pamięci i wydajnej możliwości rekonfigurowania, obsługuje skalowalne i ekonomiczne projekty w szerokiej gamie nowoczesnych zastosowań.Wspierana przez wiodące w branży wsparcie Intela, ta FPGA pozostaje niezawodnym i elastycznym rozwiązaniem do poszukiwania solidnej programowalnej logiki zarówno we wdrożeniach o niskiej, jak i środkowej objętości.

Arkusz danych pdf

EP1C4F324C7N Arkuszy danych:

All Dev PKG CHG 1/Aug/2018.pdf

Mult Dev Dessicant CHG 19/Jul/2019.pdf

Oprogramowanie Mult Series CHGS 26/MAR/2020.PDF

Virtual JTAG Megafuntion Guide.pdf

Cylindryczne uchwyty akumulatorów. PDF

O nas

ALLELCO LIMITED

Czytaj więcej

Szybkie zapytanie.

Proszę wysłać zapytanie, natychmiast odpowiemy.

Często Zadawane Pytania [FAQ]

1. Czy można zastosować EP1C4F324C7N z DDR lub SDRAM?

Tak, ta FPGA obsługuje zewnętrzne typy pamięci, w tym DDR SDram, dzięki wieloczęściowej obsłudze we/wy.Jednak układ PCB musi być zgodny z ścisłymi wytycznymi dotyczącymi pomiaru czasu i impedancji w zakresie szybkiego interfejsu pamięci.

2. Jakie są typowe wymagania mocy dla EP1C4F324C7N?

To urządzenie działa przy napięciu rdzeniowym od 1,425 V do 1,575 V, z dodatkowymi napięciami wymaganymi dla standardów we/wy.Aby uzyskać dokładne planowanie energii, użyj Intel PowerPlay Power Analyzer w Quartus, aby oszacować zużycie na podstawie projektu.

3. Czy EP1C4F324C7N ROHS jest zgodny i wolny od potencjalnych klientów?

Tak, EP1C4F324C7N jest zgodny z dyrektywami ROHS i jest dostępny w pakietach wolnych od połowie.To sprawia, że nadaje się na rynki i aplikacje regulowane dla środowiska, które wymagają certyfikacji zielonej elektroniki.

4. Jak długo trwa skompilowanie i zaprogramowanie projektu na EP1C4F324C7N?

W przypadku umiarkowanych projektów złożoności kompilacja i programowanie zwykle zajmuje od 3 do 5 minut, w zależności od wydajności komputera.Analiza pomiaru czasu i przypisania PIN mogą rozszerzyć proces, jeśli projekt wymaga ścisłych ograniczeń czasowych.

5. Czy potrzebuję specjalnych narzędzi do zaprogramowania EP1C4F324C7N?

Potrzebujesz oprogramowania Intel Quartus II, które jest dostępne w bezpłatnej edycji Lite, oraz w blasterku USB lub kompatybilnym programistom JTAG.Te narzędzia umożliwiają kompilowanie projektu, generowanie plików programowania i przesyłanie ich do FPGA.

Cyfrowy procesor sygnału GC5330izev: funkcje, aplikacje, alternatywy i specyfikacje

na 2025/04/1

Kompletny przewodnik po rezystorze 0402: specyfikacje, zastosowania i techniki lutowania

na 2025/04/1

Popularne posty

-

Złożone komputery zestawu instrukcji: Jak zmieniły obliczenia?

na 8000/04/18 147778

-

Pinout i funkcje USB-C

na 2000/04/18 112033

-

Korzystanie z prymitywnych symulacji XILINX: kompleksowy przewodnik po projekcie i symulacji FPGA

na 1600/04/18 111352

-

Napięcia zasilania w elektronice: znaczenie VCC, VDD, VEE, VSS i GND

na 0400/04/18 83790

-

RJ45 Podręcznik złącza: pinout, okablowanie, typy kablowe i zastosowania

na 1970/01/1 79596

-

Ostateczny przewodnik po kodach kolorów drutu w nowoczesnych systemach elektrycznych

Sposób, w jaki nasze systemy elektryczne używają kolorów, nie jest tylko dla wyglądu.Każdy kolor drutu wskazuje teraz określoną funkcję, ułatwiając poprawną identyfikację komponentów elektrycznych ...na 1970/01/1 66976

-

Przewodnik zaworu oczyszczania: funkcja, objawy, testowanie i wymiana w celu optymalnej wydajności silnika

Zawór czyszczenia jest kluczową częścią systemu samochodu, który pomaga utrzymać w czystości powietrza poprzez zarządzanie oparami paliwowymi, zanim będą mogły uciec do atmosfery.To nie tylko pomag...na 1970/01/1 63110

-

Jakość (Q) Współczynnik: Równania i zastosowania

Współczynnik jakości lub „Q” jest ważny podczas sprawdzania, jak dobrze induktory i rezonatory działają w systemach elektronicznych, które wykorzystują częstotliwości radiowe (RF).„Q” mierzy, jak d...na 1970/01/1 63043

-

Osiągnięcie wydajności szczytowej przy maksymalnym twierdzeniu o przeniesieniu mocy

Twierdzenie o maksymalnym przeniesieniu mocy wyjaśnia, w jaki sposób energia ze źródła, takiego jak akumulator lub generator, płynie do podłączonego obciążenia.Pokazuje dokładny warunek, w którym o...na 1970/01/1 54097

-

A23 Specyfikacje i kompatybilność baterii

Akumulator A23 to mała akumulator w kształcie cylindra o wysokim napięciu.Nazywany również 23a, 23E lub Mn21, działa przy 12 woltach i znacznie wyższy niż akumulatory AA lub AAA.Jego specj...na 1970/01/1 52197