Kompleksowy przewodnik po protokole komunikacji SPI

W tym artykule zbadamy szczegóły protokołu szeregowego interfejsu peryferyjnego (SPI), koncentrując się na jego wydajnych możliwościach przesyłania danych i wszechstronnych aplikacjach.SPI jest szybkim, synchronicznym protokołem komunikacyjnym szeroko stosowanym w systemach osadzonych do łączenia mikrokontrolerów z różnymi peryferyjami.Z konfiguracją mistrza i czterech linii podstawowych-MISO, MOSI, SCLK i CS-SSPI upraszcza komunikację danych, zapewniając jednocześnie synchronizację między urządzeniami.Zagłębiamy się w podstawowe zasady SPI, w tym dynamikę operacyjną, konfigurację sprzętu, diagramy czasowe i praktyczne porady konfiguracji.Niezależnie od tego, czy jesteś nowy w SPI, czy chcesz udoskonalić swoje zrozumienie, ten post zapewni cenne wgląd w maksymalizację jego potencjału w rzeczywistych zastosowaniach.Katalog

Przegląd protokołu SPI

Serialny interfejs peryferyjny (SPI) wykorzystuje system 4-wire, który usprawnia operacje procesora poprzez zmniejszenie kosztów oprogramowania.Znany ze swojej szybkości i wydajności, SPI jest podstawowy w urządzeniach takich jak AT91RM9200.W ramach mistrzów mistrzów mistrz rządzi zadaniami, łącząc się z niewolnikami przez cztery potrzebne przewody: MISO (Master in Slave Out), MOSI (Master Out Slave IN), SCLK (zegar szeregowy) i CS (Chip Select).Linia MISO kanał dane z powrotem do głównego, podczas gdy MOSI zarządza danymi wychodzącymi.SCLK zapewnia sygnały zegara z Master, a CS ułatwia kontrolę aktywacji urządzenia.Prostota SPI sprawia, że jest to głównie przydatne do łączenia wielu urządzeń w jednej magistrali, wykonywanie przesyłania danych seryjnie i osiąganie synchronizacji za pomocą impulsów zegara.Tutaj Master może zatrzymać komunikację bez wpływu na niezawodność danych.Podczas gdy SPI nie ma funkcji kontroli przepływu i uznania danych, jego zdolność do rozszerzania połączeń peryferyjnych poprzez zewnętrzne dekodery rekompensuje te ograniczenia.

Specyficzne przypadki wykorzystania SPI

SPI jest zbudowany wokół charakterystycznej konfiguracji magistrali pierścieniowej przy użyciu części takich jak SS (CS), SCK, SDI i SDO do wymiany danych rejestru.Na przykład 8-bitowy transfer rejestru wykorzystuje krawędzie zegara do zarządzania ruchem danych i rejestracji zmian.Inicjalizacja w konfiguracji mistrza-niewolnika rozpoczyna się od wstępnej konfiguracji buforów nadawców transcemiiły, ilustrując proces komunikacji.SPI Motorola wyróżnia się synchroniczną komunikacją szeregową, wykorzystując MOSI, MISO i SCK do zaawansowanych zadań send-receive, elastyczności wśród ról mistrzowskich i solidnych funkcji zegara.Urządzenia muszą synchronizować fazę zegara i polaryzację spójności komunikacji.Z zdolnością łączenia do 256 portów, SPI koncentruje się na łączności punkt-punkt i transfer danych opartych na pakiecie.

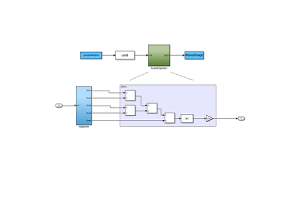

Formułowanie logiki użytkownika

Projektowanie logiki użytkownika elastycznego jest dynamiczne dla aplikacji zawierających struktury wieloosobowe.W konfiguracji podwójnego portu niezależne FIFOS obsługują dane dotyczące adresów portów.Jednocześnie arbitraż logiczny nadzoruje fragment danych do interfejsu SPI4, uwzględniając dane natychmiastowe kontroli przepływu i statusy FIFO.

SPI Dynamika operacyjna

SPI jest zaprojektowany w celu niezawodnej komunikacji, zawierający dyskretne kanały do danych i kontroli przepływu podczas transmisji.Rozległa łączność portów pozwala na przesyłanie danych opartych na pakiecie, zapewniając weryfikację punkt-punkt za pośrednictwem adresów pakietów, w ten sposób poszerzając wszechstronność aplikacji.

Badanie diagramów czasowych przesyłania danych

Interfejsy SPI charakteryzują się czterema diagramami czasowymi zależnymi od ustawień CPOL i CPHA.CPOL definiuje stan bezczynności dla SCK, podczas gdy CPHA wyznacza krawędź zegara próbkowania.Te konfiguracje są aktywne w celu zapewnienia dokładności danych i synchronizacji.

Synchroniczna komunikacja szeregowa

Pochodzący z Motoroli, SPI stanowi czterokierunkową, dwukierunkową magistrację seryjną zaprojektowaną do szybkiej komunikacji synchronicznej, łącząc mikrokontrolery z peryferyjami, takimi jak EEPROM, RTC i konwertery A/D.Sieć SPI umiejętnie łączy mieszane urządzenia peryferyjne, wykorzystując protokoły, które pomijają mechanizmy adresu dla bezpośredniej wymiany pełnego dupleksu.Dodatkowe linie, takie jak INT, mogą poprawić reaktywność systemu.

Zawiłości konfiguracji sprzętowej

Pomimo biegłości SPI w interfejsie z różnymi peryferyjami, indywidualne sygnały włączające dla każdego urządzenia powodują złożoność w porównaniu z prostszymi systemami, takimi jak I2C.Ta złożoność jest wewnętrznym aspektem konfiguracji sprzętowej SPI, zawierającego rejestry zmiany biegów dla 8-bitowych transferów danych.Podczas pracy urządzenia przesuwają bity przesuwane przez rejestry za pomocą spadającej krawędzi zegara.

Ocena zdolności i praktyczności

Wykorzystując elementy takie jak Spiclk, MOSI, MISO i NSS, sieci SPI ustanawiają role mistrzowskie oparte na stanach PIN NSS.Wspierając środowiska pojedynczych lub wielu mistrzów, protokół dostosowuje się do kontroli do 16 urządzeń peryferyjnych.Chociaż brakuje mu metod kontroli przepływu i potwierdzenia, struktura protokołu skutecznie uwzględnia różnorodne konfiguracje połączeń i komunikacji.

Ilustracje konfiguracji i czasu

Transakcje danych SPI są regulowane przez proste reguły czasowe pod wpływem zarządzania SCK.Na przykład wzorzec rejestru, taki jak 10101010, wysyła dane bit-bit za pomocą zmian napędzanych zegara, podkreślając dynamikę uproszczenia i przejścia danych w magistrali pierścieniowej.

Rozszerzone spostrzeżenia na temat wydajności

Właściwa synchronizacja fazy zegara SPI i polaryzacji na urządzeniach głównych i niewolniczych jest wykorzystywana do ciągłych transakcji danych.Parametry takie jak CPOL i CPHA powinny wyrównać urządzenia w systemach związanych ze SPI w celu utrzymania harmonii komunikacji.

Praktyczne porady konfiguracyjne

Korekty konfiguracji zegara SPI muszą wziąć pod uwagę wymagania zegara urządzenia niewolnika, aby zapewnić dokładność danych podczas cykli transferu.Rozpoznanie krawędzi sygnału podczas transferów danych jest poważne, aby zapobiec niespójnościom połączeń.Podręczniki produktu często szczegółowo opisują wymagane ustawienia, podkreślając wpływ precyzyjnego wyrównania Fathing na dokładność transmisji.

Podstawy komunikacji SPI

U podstaw szeregowego interfejsu peryferyjnego (SPI) służy jako pełny, synchroniczny protokół komunikacji szeregowej, wymagając wcześniej ustaleń dotyczących interakcji.Ta funkcja wyróżnia się, z natury podkreślając zsynchronizowane wymiany.Godnym uwagi aspektem SPI jest poleganie na modelu mistrza, w którym urządzenie główne organizuje kontrolę poprzez generowanie sygnałów zegara i inicjowanie sesji komunikacyjnych.Natomiast urządzenia niewolników pozostają ostro dostrojone do tych sygnałów, gotowe uczestniczyć po wezwaniu.

Mechanizm współpracy między urządzeniami mistrzem i niewolnikami w SPI jest skrupulatnie zorganizowany.Mistrz ponosi wyłączną odpowiedzialność za zarządzanie zegarami, zapewniając stały rytm wymiany danych.Ten nadzór usprawnia synchronizację, eliminując nieprzewidywalność często występującą w systemach asynchronicznych.Ustanawiając zjednoczone odniesienie do czasu, oba urządzenia mogą wykonać operacje z dokładnością, praktyką udoskonaloną poprzez obszerne doświadczenie aplikacji.Uporządkowany charakter SPI zapewnia wydajne możliwości transferu danych, stanowiąc prostą alternatywę dla bardziej skomplikowanych protokołów.

Ramy SPI ujawnia szczególne ograniczenia, szczególnie w ustawieniach, które podkreślają łatwość plug-and-play.Nieelastyczny charakter jego protokołu oznacza, że kompatybilność musi zostać skrupulatnie ułożona z góry.Urządzenia w ramach funkcji konfiguracji SPI pod władzą sygnałów zegara i określonych umów protokołu.Chociaż upraszcza to synchronizację, wymaga wstępnych wysiłków konfiguracji.Umiejętne zastosowanie tych zasad wykazało potencjał złagodzenia rozbieżności komunikacji.Jak zaobserwowano w ocenach sesji, zrozumienie rygoru strukturalnego SPI nie tylko zwiększa praktyczne wdrożenie, ale także zwiększa dokładność zastosowania.

O nas

ALLELCO LIMITED

Czytaj więcej

Szybkie zapytanie.

Proszę wysłać zapytanie, natychmiast odpowiemy.

Wszystko o UDP: Przewodnik po komunikacji bez połączeń

na 2024/12/30

Technologia HD: zwiększenie doskonałości wizualnej

na 2024/12/30

Popularne posty

-

Złożone komputery zestawu instrukcji: Jak zmieniły obliczenia?

na 8000/04/18 147758

-

Pinout i funkcje USB-C

na 2000/04/18 111941

-

Korzystanie z prymitywnych symulacji XILINX: kompleksowy przewodnik po projekcie i symulacji FPGA

na 1600/04/18 111349

-

Napięcia zasilania w elektronice: znaczenie VCC, VDD, VEE, VSS i GND

na 0400/04/18 83721

-

RJ45 Podręcznik złącza: pinout, okablowanie, typy kablowe i zastosowania

na 1970/01/1 79508

-

Ostateczny przewodnik po kodach kolorów drutu w nowoczesnych systemach elektrycznych

Sposób, w jaki nasze systemy elektryczne używają kolorów, nie jest tylko dla wyglądu.Każdy kolor drutu wskazuje teraz określoną funkcję, ułatwiając poprawną identyfikację komponentów elektrycznych ...na 1970/01/1 66914

-

Przewodnik zaworu oczyszczania: funkcja, objawy, testowanie i wymiana w celu optymalnej wydajności silnika

Zawór czyszczenia jest kluczową częścią systemu samochodu, który pomaga utrzymać w czystości powietrza poprzez zarządzanie oparami paliwowymi, zanim będą mogły uciec do atmosfery.To nie tylko pomag...na 1970/01/1 63064

-

Jakość (Q) Współczynnik: Równania i zastosowania

Współczynnik jakości lub „Q” jest ważny podczas sprawdzania, jak dobrze induktory i rezonatory działają w systemach elektronicznych, które wykorzystują częstotliwości radiowe (RF).„Q” mierzy, jak d...na 1970/01/1 63012

-

Osiągnięcie wydajności szczytowej przy maksymalnym twierdzeniu o przeniesieniu mocy

Twierdzenie o maksymalnym przeniesieniu mocy wyjaśnia, w jaki sposób energia ze źródła, takiego jak akumulator lub generator, płynie do podłączonego obciążenia.Pokazuje dokładny warunek, w którym o...na 1970/01/1 54081

-

A23 Specyfikacje i kompatybilność baterii

Akumulator A23 to mała akumulator w kształcie cylindra o wysokim napięciu.Nazywany również 23a, 23E lub Mn21, działa przy 12 woltach i znacznie wyższy niż akumulatory AA lub AAA.Jego specj...na 1970/01/1 52135